# Development of Electronics for the Hyper-Kamiokande Experiment

Marcin Ziembicki

(Warsaw University of Technology)

For

Hyper-Kamiokande Proto-Collaboration

International Workshop on Next Generation Nucleon Decay and Neutrino Detectors (NNN'16) November 3-5, 2016, Bejing, China

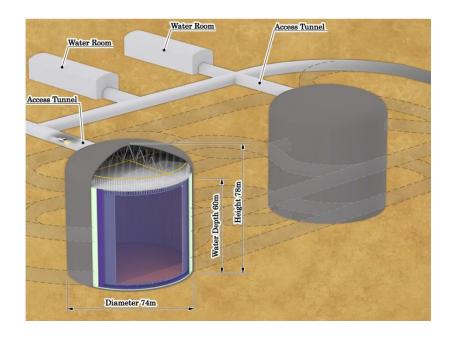

### Introduction – Hyper Kamiokande

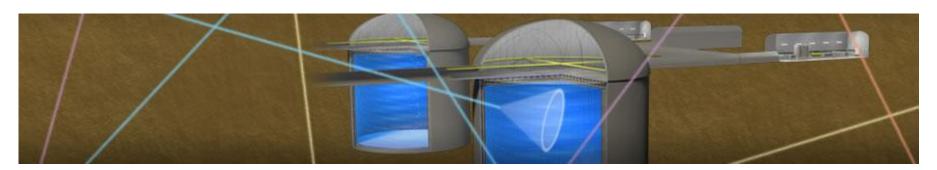

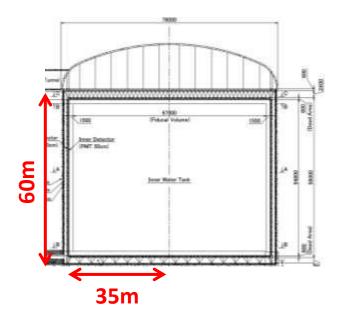

- Giant underground water Cherenkov Detector

- − Two tanks,  $\varnothing$ =74m, H=60m

- ≈520kt of ultrapure water

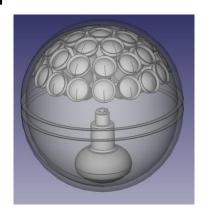

- 93,400 photo-sensors (80,000 ID + 13,400 OD)

- Role of photo-sensors and electronics:

- Measure charge and timing of pulses coming from Cherenkov photons.

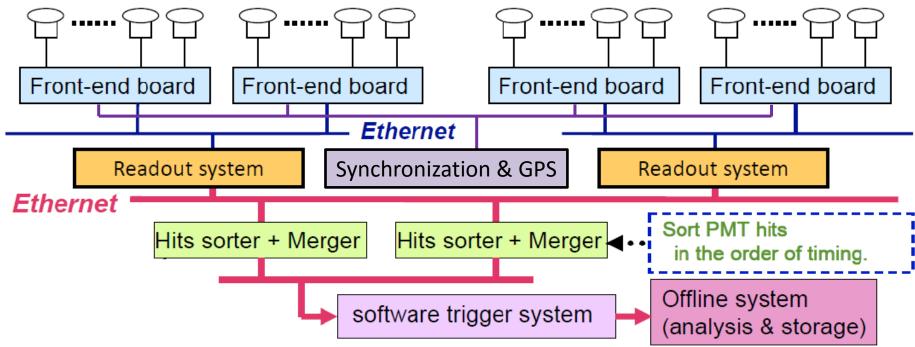

### Overview of the System

- Self-triggering system

- Digitize all photo-sensor signals above discriminator threshold

- Send hit information to readout computers

- Use software trigger for event selection & send them to offline system for storage

- Accurate clock synchronization and GPS

- Stable power supplies (photo-sensors, other systems)

#### Location of Frontend Electronics

#### Option 1 – detector's roof

#### **ADVANTAGES:**

- Serviceability

- More options for accommodating power-hungry electronics

#### **DISADVANTAGES:**

- Length of cables:

- $-40 \text{ m} \text{ (bottom)} + 65 \text{ m} \text{ (wall)} + 40 \text{ m} \text{ (surface)} \approx 150 \text{ m}$

- Expect degradation of the signal

- Different length of cables may make calibrations difficult

- Weight of cables

- $-100\sim200 \text{ g/m} \rightarrow 150 \text{ m} \cong 15\sim30 \text{ kg} \rightarrow 675\sim1350 \text{ tons!}$

- Non-negligible weight

- Affects design & cost of the structure

#### Location of Frontend Electronics

#### Option 2 – water (current baseline design)

#### **ADVANTAGES:**

- Shorter cables

- Better signal quality

- Smaller number of cables

- Savings on weight and structure costs

#### **DISADVANTAGES:**

- Hydrostatic pressure at the bottom of the tank (~6 atm)

- Poor to none serviceability

- Extreme reliability is a must!

- Limits for power consumption

- Heat dissipation affects water circulation

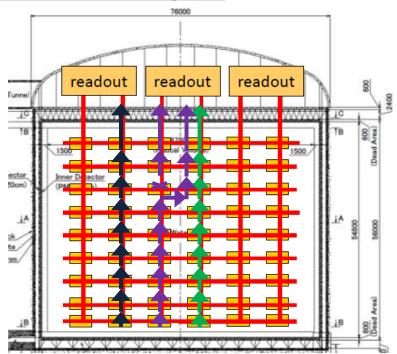

#### Mesh-type connection

- Avoid single point of failure

- Lower module transmits data to upper module; if unable, then to its neighbors

- On-going R&D on protocol and expected data rates

#### **Cables and Connectors**

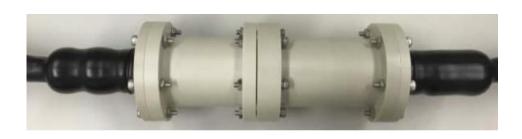

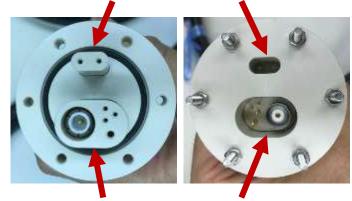

#### **R&D** on water-tight connector

- HV lines (up to 10kV)

- LV, GND & signal lines

HV lines (up to 10kV)

LV, GND and signal lines

Design of the outer shell is universal and can accommodate various connectors, e.g. Ethernet, optical fibers, power lines.

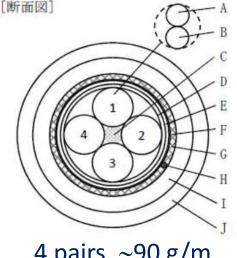

#### **Pressure tolerant Ethernet cable**

Prototype ordered, tests are on-going!

Standard Ethernet cable is unsuitable, because it gets compressed and does not transmit differential signal properly.

4 pairs, ~90 g/m

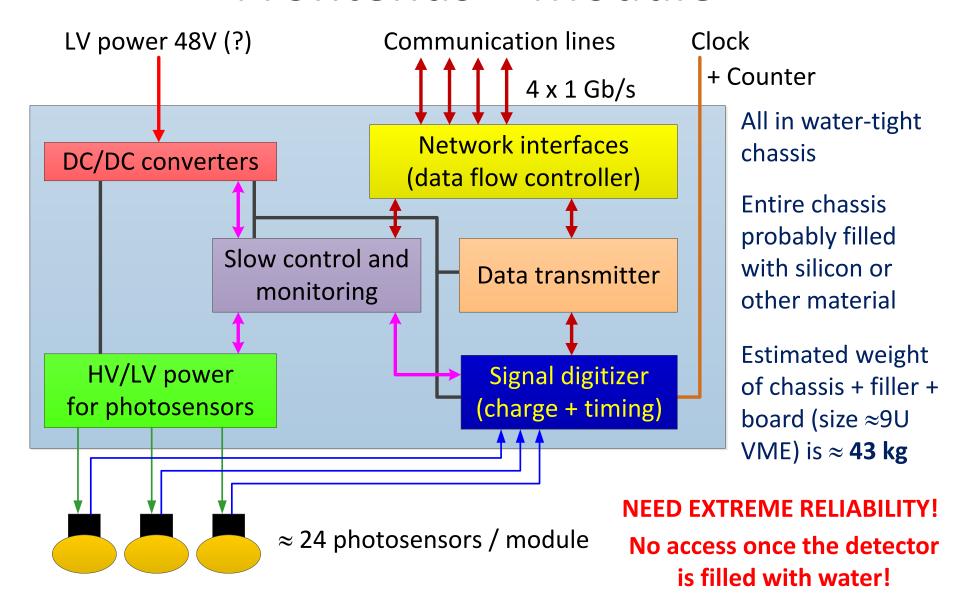

#### Frontends – Module

### Frontends – Reliability

- Need reliable operation for approx. 20 years

- Extensive R&D foreseen to identify most risky components

- What is the risk of failure?

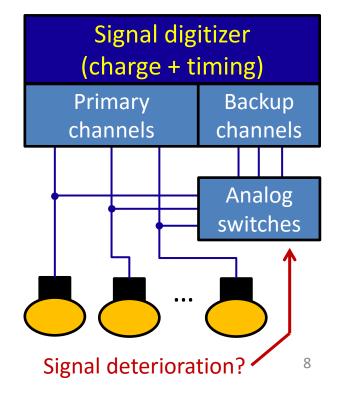

- Should certain elements be redundant?

- How to provide redundancy and at what cost?

#### **HV SUPPLY** HV/LV power HV/LV power for photosensors for photosensors Do we make HV supplies redundant? If so, what would be the cost and extra power? How to couple two supplies into a single HV channel? Use Diodes? Is it at all possible for HPD (8kV)? Will we actually increase reliability?

#### SIGNAL ACQUISITION

### Digitization Requirements

- Performance determined by photo-sensors and not by readout

- $\sigma$ (time) < 10% of photo-sensor TTS;  $\sigma$ (charge) < 0.05 pC.

- No dead time (or at least minimized dead time)

$BW \cong \frac{0.35}{t_r}$

Self triggering

:···> Talk by Nakayama-san

$t_r = 10\%-90\%$  rise time

20" High QE Box&Line PMT

$t_r = 6.8 \text{ ns}$ BW  $\cong 52 \text{ MHz}$ TTS 1 p.e.  $(\sigma) = 1.7 \text{ ns}$

20" High QE HPD with Ø20mm AD

(\*)  $t_r = 16 \text{ ns}$   $BW \cong 22 \text{ MHz}$ TTS 1 p.e.  $(\sigma) = 1.6 \text{ ns}$

multi-PMT (specs. for 3" PMTs)

$t_r = \sim 2.5 \text{ ns}$ BW  $\cong 140 \text{ MHz}$ TTS 1 p.e.  $(\sigma) < 1 \text{ ns } (?)$

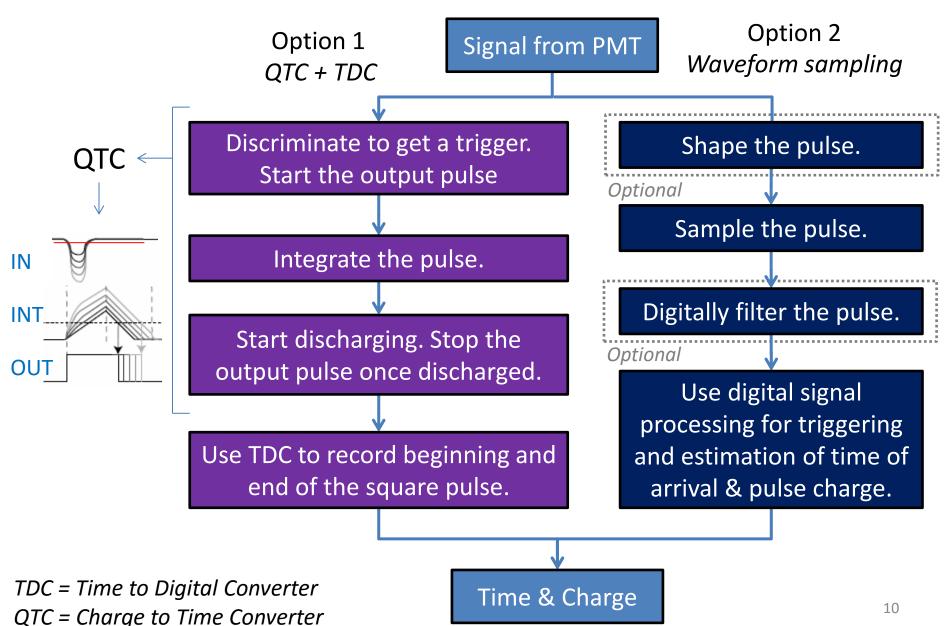

### Digitization Options

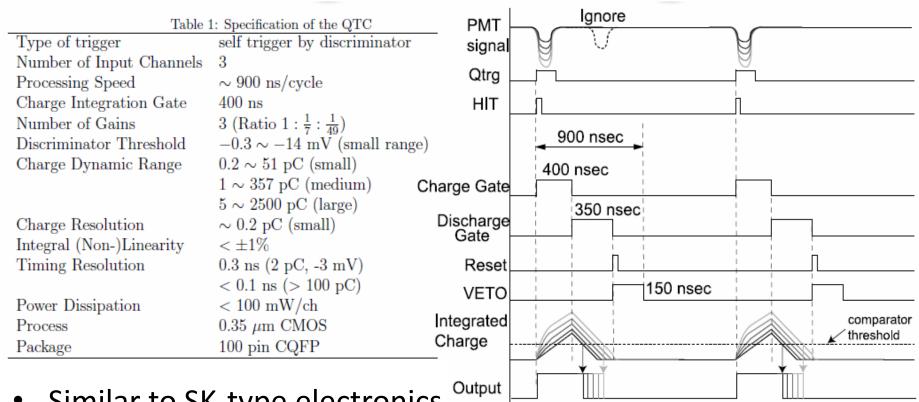

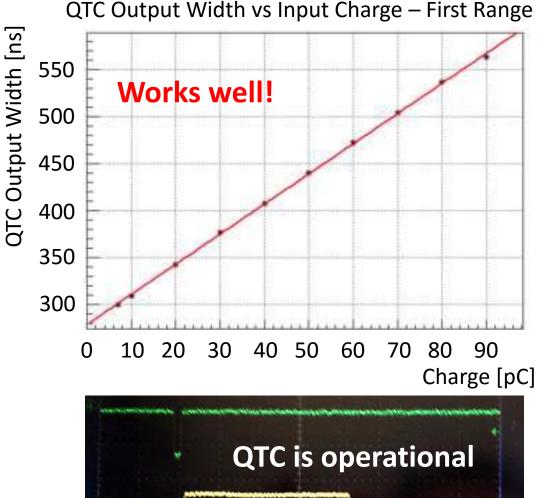

### Digitization – QTC + TDC

- Similar to SK-type electronics

- Uses custom built QTC ASIC and external TDC

- 3 QTC channels per one PMT channel

- Necessary to cover wide dynamic range

- Process rule is CMOS 0.35 μm still possible to manufacture the same chip. However, TDC chip is no longer available.

Works well in SK! (QBEE board)

#### Digitization – QTC + TDC

- Considering to use FPGAbased TDC

- FPGA-based "Wave Union" TDC by Jin-Yuan Wu, Fermilab

- QTC test board was designed and fabricated at FNAL/BU

- Works with FPGA

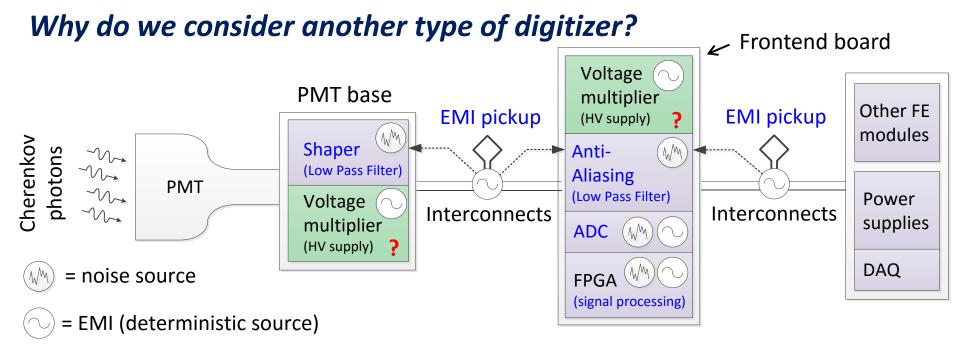

### Digitization – Waveform Sampling

- Possibility to implement completely dead-time free system.

- Better ability to tag decay electrons that occur at short decay times and high muon energies.

- Can subtract off periodic EMI by digital filters implemented in FPGA firmware.

- There is a price to pay: power consumption and cost (?).

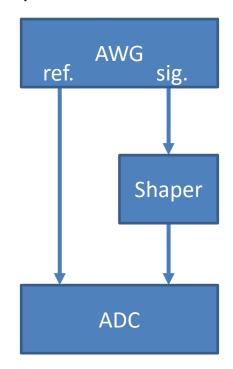

#### Timing Resolution of Sampling Digitizers

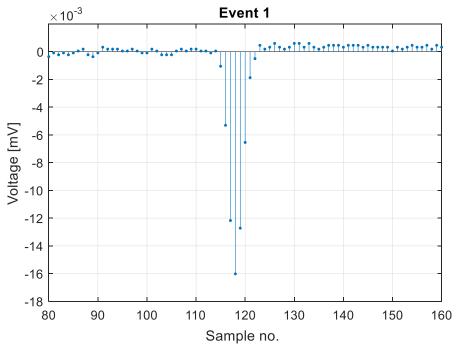

#### **PURPOSE OF THE STUDY:**

Determine how fast and how precise does a system needs to be to achieve given performance specs?

- Use AWG instead of PMT.

- Use large reference pulse (timing accuracy  $\sigma \approx 10$  ps) and small, shaped signal pulse (1 mV  $\sim 100$  mV).

- Apply signal processing methods and calculate time difference Δt between ref. and sig. channels.

- Repeat multiple times and compute RMS of Δt values.

- Two shapers:

- 15 ns and 30 ns rise time

(10% to 90%), 5-th order

Bessel-type low-pass filters.

Agilent 33600A (1 GSPS/80 MHz)

**Custom shapers**

Commercial ADCs (CAEN)

V1720 (250 MSPS/12b)

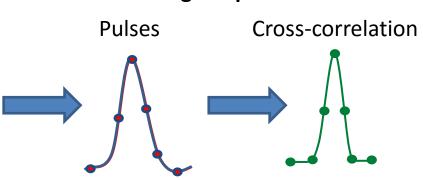

### Signal Processing Methods

Value

0.02

0.01

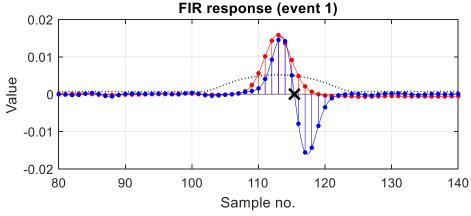

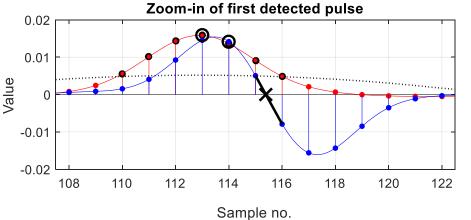

Optimal Zero-Average FIR Filter

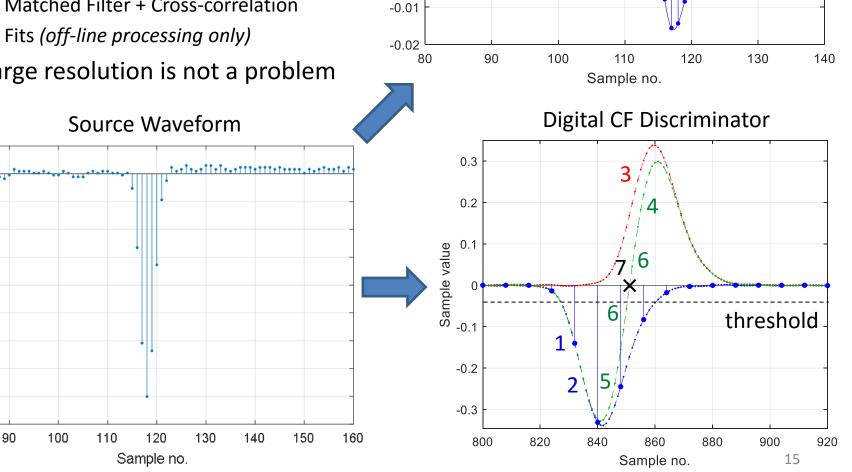

- Tested four methods of time estimation:

- **Digital Constant Fraction Discriminator**

- Optimal Zero-Average FIR Filter

- Matched Filter + Cross-correlation

- Fits (off-line processing only)

$\times 10^{-3}$

-2

Voltage [mV]

-12

-14

-16

-18 80

Charge resolution is not a problem

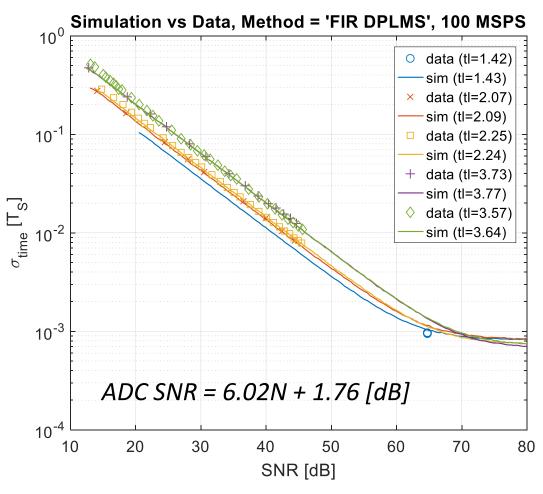

### Results of Timing Resolution Study

- We can easily determine time with precision well below the sampling period

- Determining factors are:

- System bandwidth (limits) sharpness of pulse edge)

- Signal-to-noise ratio

- Signal processing methods

- Can improve SNR with oversampling and proper filtering

Extensive effort has been put into developing electronics models.

They match data well, so we now have tools to easily try more shaper & ADC variants. 16

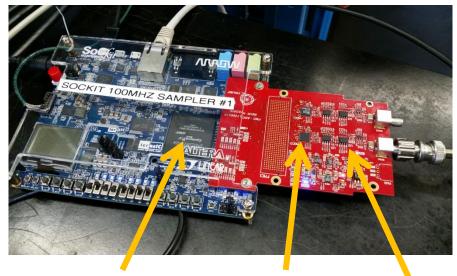

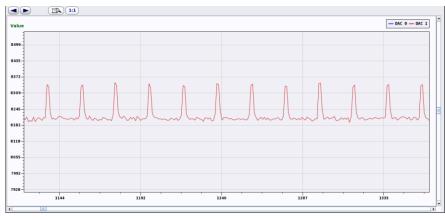

#### **FADC** Prototype

- First prototype designed and built

- 100 MSPS FADC + 15 ns shaper

- Low power Flash-ADC for 20" photo-sensors

- 0.55W per channel (excluding FPGA), but possible to get down to 0.4W/channel.

- Can get further reduction of power consumption if an 80 MSPS ADC is chosen.

- Will start analysis of the data soon.

ALTERA Cyclone V SoC evaluation card ADC LT2260

Shaper

Sample waveform with periodic pulses

Cyclone V SoC = Cyclone V FPGA

Cortex-A9 ARM processor

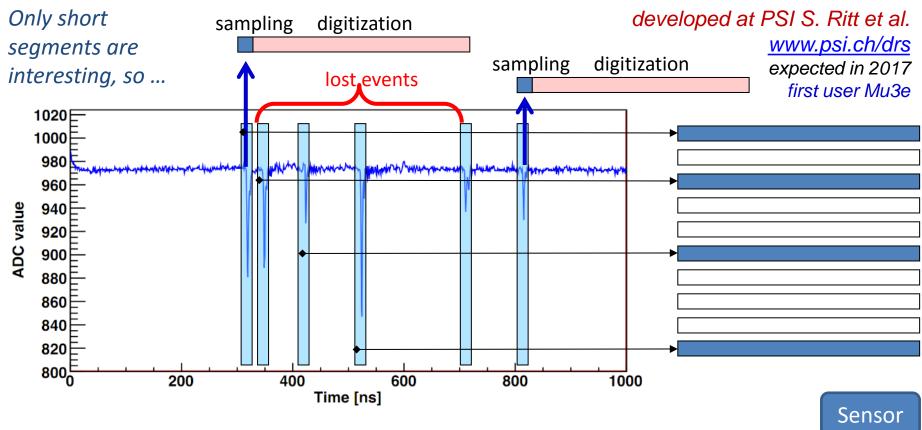

### **Switched Capacitor Arrays**

#### **DRS5** solution:

- Store continuously sampled waveform in a 2D array

- Digitize only interesting segments (f<sub>s</sub> ~ 1GHz)

- Sampling and digitization asynchronous

- Virtually dead-time less up to average rate = f<sub>ADC</sub> / window size

### Summary

- Experience from Super-Kamiokande is useful in designing new system

- On-going R&D on individual components to maximize detector performance and reliability while minimizing the cost

- Water-tight connectors

- Pressure-tolerant cables compatible with ultra-pure water

- High voltage supplies

- Digitization options

- Reliability of all the components

- And many, many more...

## LET US KNOW IF YOU WOULD LIKE TO JOIN THE EFFORT! YOU ARE VERY WELCOME!

#### **BACKUP**

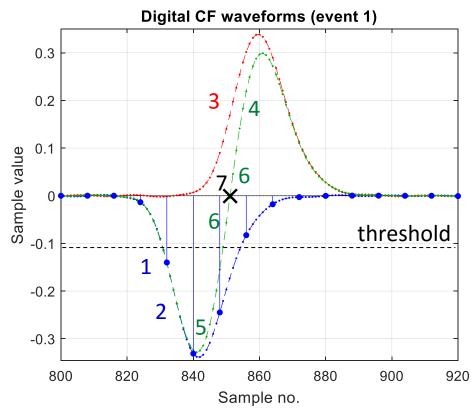

### Signal Processing Methods

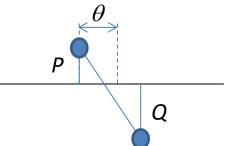

### **Digital Constant Fraction Discriminator:**

- Simple processing → needs little

FPGA resources

- Does not make any assumption as to the pulse shape

- Favors high sampling rate, but some improvements are possible for low sampling rates if pulse shape is invariant

- Poor performance in low SNR conditions

Time errors and possible correction

$\theta$ - actual sub-sample shift

$$CR = \frac{P}{P - Q}$$

### Signal Processing Methods II

#### **Zero-Average Optimal FIR Filter:**

- More complex processing

- Works well with filter orders of 9-12

- Assumes that shape is invariant

- Better behavior at low SNR

### Signal Processing Methods III

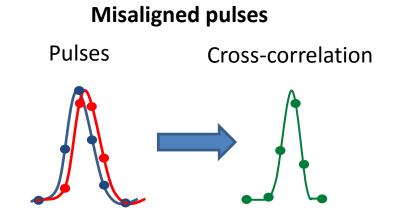

#### **Matched FIR Filter and Cross-Correlation Processing:**

- Much more complex processing

- Works well with filter orders of 9-12

- Assumes that shape is invariant

- Similar timing performance to zeroaverage FIR filter

- Relatively easy to disentangle piled-up pulses

Sub-sample shifts done using windowed sinc interpolation (Blackman window). FFT interpolation also possible if shifting impulse response.

#### **Aligned pulses**