#### Pixel design and prototype characterization in China

#### Yunpeng Lu

#### On behalf of Vertex sub-detector group

Nov. 13, 2018 / Beijing

## Outline

#### Introduction

- CEPC Silicon tracker

- Fine pixel

- JadePix1/2, MIC4, CPV1/2

- Pixelated strip

- SUPIX

- Summary

Note1: This talk covers only the pixel chips developed specifically for the CEPC, while other developments such as for X-ray applications are not included.

Note2: A fast timing pixel scheme to be presented by W. Wei in the TDAQ session

#### **CEPC and Its Beam Timing**

|                                                                    | Higgs                    | W                         | Z (3T)                             | Z (2T)             |  |

|--------------------------------------------------------------------|--------------------------|---------------------------|------------------------------------|--------------------|--|

| Center-of-mass energy (GeV)                                        | 240                      | 160                       | 93                                 | L                  |  |

| Number of IPs                                                      | 2                        |                           |                                    |                    |  |

| Luminosity/IP (10 <sup>34</sup> cm <sup>-2</sup> s <sup>-1</sup> ) | 3                        | 10                        | 16                                 | 32                 |  |

| Number of years                                                    | 7                        | 1                         | 2                                  |                    |  |

| Total Integrated Luminosity (ab <sup>-1</sup> ) -<br>2 IP          | 5.6                      | 2.6                       | 8                                  | 16                 |  |

| Total number of particles                                          | $1 \times 10^{6}$        | 2×10 <sup>7</sup>         | 3×10 <sup>11</sup>                 | 7×10 <sup>11</sup> |  |

| Bunch numbers<br>(Bunch spacing)                                   | 242<br>( <b>680 ns</b> ) | 1524<br>( <b>210 ns</b> ) | 12000<br>( <b>25ns + 10% gap</b> ) |                    |  |

- Continuous colliding mode

- Duty cycle ~ 50% @ Higgs, close to 100% @ W/Z

- General requirement on the detector development:

- Precise measurement, Low power, Fast readout, Radiation-hard

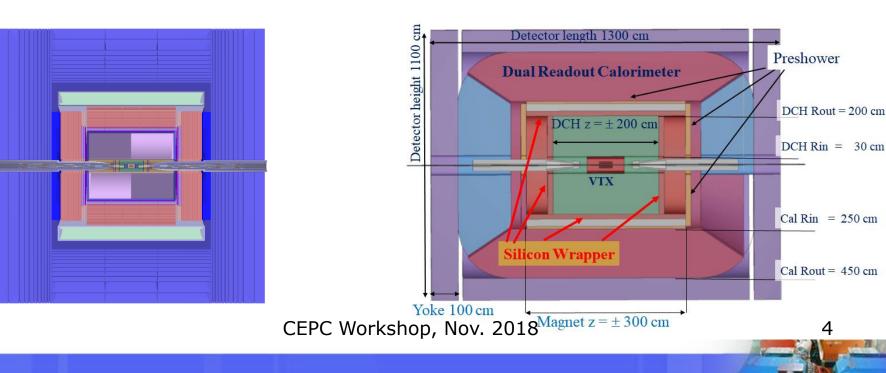

#### **Two Detector Concepts**

- Baseline detector concept

- Silicon tracker + TPC

- or Full Silicon Tracker

- High granular calorimetry system

- 3 Tesla solenoid

- Muon detector

- Alternative detector concept, IDEA

- Silicon pixel + Drift Chamber

- 2 Tesla solenoid

- Dual readout calorimeter

- Muon chamber

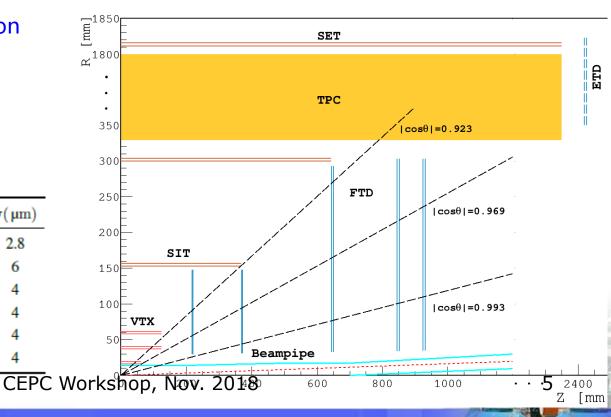

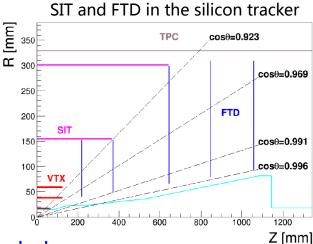

#### **Baseline Silicon Tracker Layout**

- Tracking part: Mainly microstrip

- SIT, SET, ETD, and 3 outer disks of FTD, ETD: single-sided strips mounted back to back

- 2 inner disks of FTD: pixel

- Vertex part: 3 double-sided pixel layers

- Layer 1: best s.p. resolution

- Layer 2: very fast readout

| VTX parameters |        |         |                 |                 |  |  |  |  |  |

|----------------|--------|---------|-----------------|-----------------|--|--|--|--|--|

|                | R (mm) | z  (mm) | $ \cos \theta $ | $\sigma(\mu m)$ |  |  |  |  |  |

| Layer 1        | 16     | 62.5    | 0.97            | 2.8             |  |  |  |  |  |

| Layer 2        | 18     | 62.5    | 0.96            | 6               |  |  |  |  |  |

| Layer 3        | 37     | 125.0   | 0.96            | 4               |  |  |  |  |  |

| Layer 4        | 39     | 125.0   | 0.95            | 4               |  |  |  |  |  |

| Layer 5        | 58     | 125.0   | 0.91            | 4               |  |  |  |  |  |

| Layer 6        | 60     | 125.0   | 0.90            | 4               |  |  |  |  |  |

|                |        |         |                 | CED             |  |  |  |  |  |

#### **Performance Requirements**

B = 3T

Momentum Resolution:  $\sigma_{1/p_T} = 2 \times 10^{-5} \oplus 1 \times 10^{-3} / (p_T \sin \theta)$ Impact Parameter Resolution:  $\sigma_{r\phi} = 5 \mu m \oplus \frac{10}{p(GeV) \sin^{3/2} \theta} \mu m$

#### Vertex specifications:

- $\sigma_{SP}$  near the IP:  $\leq 3 \mu m$

- Material budget:  $\leq$  0.15% X <sub>0</sub> / layer

- First layer located at a radius: ~1.6 cm

- Pixel occupancy:  $\leq 1 \%$

#### Tracking specifications:

- $\sigma_{SP}$  :  $\leq 7 \ \mu m$

- Material budget:  $\leq$  0.65% X <sub>0</sub> / layer

#### **Pixel Sensor Specifications**

- To achieve single point resolution

- Pixel size ~ 16 μm (Binary readout)

- To lower the material budget

- Sensor thickness ~ 50  $\mu$ m

- Air cooling, heat load < 50 mW / cm<sup>2</sup>

- To tackle beam-related background

- Fast readout 1 ~ 100  $\mu s$  / frame

- 3.4Mrad / year & 6.2×10<sup>12</sup>n<sub>eq</sub> / (cm<sup>2</sup>·year)?

| Physics driven requirements                  | <b>Running constraints</b> | Sensor specifications                                                                                     |

|----------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------|

| $\sigma_{s.p.} = 2.8 \mu m$                  |                            | > Small pixel 16 µm                                                                                       |

| Material budget 0.15% X <sub>0</sub> / layer |                            | > Thinning 50 μm                                                                                          |

|                                              | > Air cooling              | > Low power 50 mW / cm <sup>2</sup>                                                                       |

| r of Inner most layer                        | > beam-related background  | d ·····> Fast readout 1 ~ 100 µs                                                                          |

| L                                            | 5                          | > Radiation tolerance<br>3.4 Mrad / year<br>6.2×10 <sup>12</sup> n <sub>eq</sub> / (cm <sup>2</sup> year) |

|                                              | CEPC Workshop, Nov. 2018   | 6.2×10 <sup>+2</sup> n <sub>eq</sub> / (cm <sup>2</sup> year)                                             |

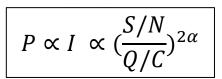

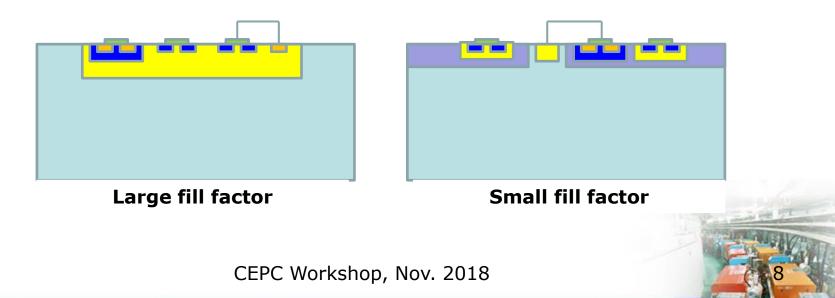

# Key factors to low power design

- Depleted sensing diode

- Signal charge Q ↑ or cluster size ↓

- Capacitance of the input node ↓

- Small fill factor

- Capacitance of the input node  $\downarrow$

- In pixel discriminator

- Eliminate the large driving current of analog output

$\alpha$  = 2 for strong inversion,  $\alpha$  = 1 for weak inversion

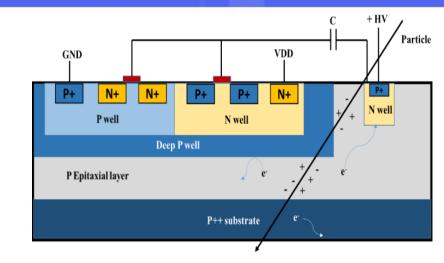

# **Pixel technologies**

- CMOS pixel sensor (CPS)

- TowerJazz CIS 0.18 µm process

- Quadruple well process

- Thick (~20 µm) epitaxial layer

- with high resistivity ( $\geq 1 \text{ k}\Omega \cdot \text{cm}$ )

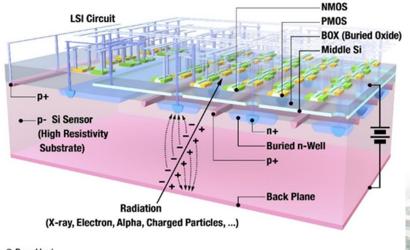

- SOI pixel sensor

- LAPIS 0.2 µm SOI process

- High resistive substrate ( $\geq 1 \text{ k}\Omega \cdot \text{cm}$ )

- Double SOI layers available

- Thinning and backside process

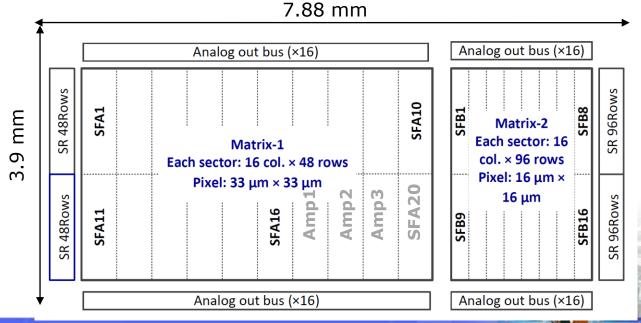

#### CMOS Prototype: JadePix1 (Team in IHEP)

- Diode optimization and radiation hardness study

- Two independent matrices:

- Matrix-1:  $33 \times 33 \ \mu m^2$  pixels

- Matrix-2:  $16 \times 16 \mu m^2$  pixels.

- A variety of diode geometries

- Matrix-1: 20 sectors, each sector includes 48 rows and 16 columns.

- Matrix-2: 16 sectors, each 96 rows and 16 columns.

- Analog readout

- Source follower or voltage amplifier

- Multiplexed to 16 analog output ports

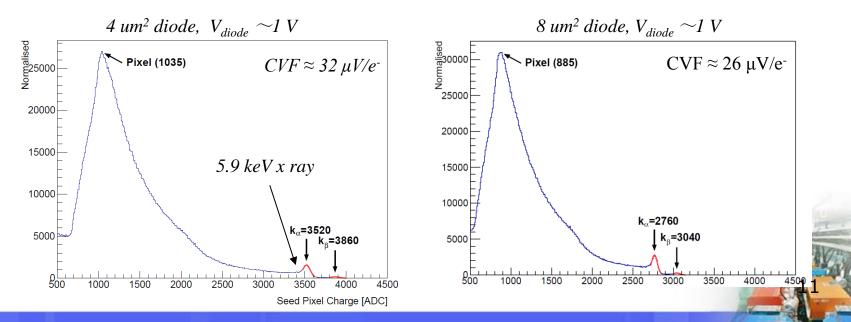

## **Measurement of Diode Capacitance**

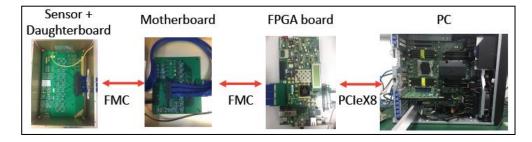

- JadePix1 readout system developed at IHEP

- <sup>55</sup>Fe calibration

- $K_{\alpha} = 5.9 \text{ keV}, K_{\beta} = 6.5 \text{ keV}$

- Charge Voltage Factor (CVF)

- $C_{in} = C_d + C_{parasitic}$

- $C_{in} = 5 \text{ fF on } 4 \mu m^2 \text{ diode}$

- $C_{in} = 6.15 \text{ fF on } 8 \,\mu\text{m}^2 \text{ diode}$

## **Performance after Irradiation**

Signal [ADC] 10000 10000 8000 **A1** JadePix-1 samples irradiated in neutron reactor to 10<sup>12</sup>, 5×10<sup>12</sup> and 10<sup>13</sup> 1MeV 8000 n<sub>eq</sub>/cm<sup>2</sup> 6000 Larger diode (A3 > A1) more radiation hard CEPC JadePix-1 4000 10<sup>12</sup> 1 MeV n<sub>eq</sub>/cm<sup>2</sup> 5x10<sup>12</sup> 1 MeV n<sub>eq</sub>/cm<sup>2</sup> as expected 10<sup>13</sup> 1 MeV n<sub>eq</sub>/cm<sup>2</sup> Less charge collected within the-2000 cluster at high radiation levels 0 25 10 15 20 Cluster Size [pixel] Normlized Entries 0.0 0.0 Normlized entries 0.05 0.012 A3 A1 80.0015 R 0.003 0.0005 12000 6800 7000 7200 7400 7600 7800 8000 8200 8400 Seed Pixel Charge [ADC Calibration peaks visible after CEPC JadePix-1 0.01 0.005 10<sup>12</sup> 1 MeV n<sub>ea</sub>/cm<sup>2</sup> CEPC JadePix-1 5x10<sup>12</sup> 1 MeV neg/cm<sup>2</sup> 10<sup>13</sup> 1 MeV n<sub>eg</sub>/cm<sup>2</sup> 10<sup>12</sup> 1 MeV n<sub>er</sub>/cm<sup>2</sup> 0.005 5x10<sup>12</sup> 1 MeV n<sub>er</sub>/cm<sup>2</sup> 10<sup>13</sup> 1 MeV n<sub>ed</sub>/cm<sup>2</sup>  $0^{-}$ 2000 6000 8000 10000 12000 14000 2000 4000 6000 8000 'n 4000 10000 12000 14000 12 Signal [ADC] Seed Pixel Charge [ADC]

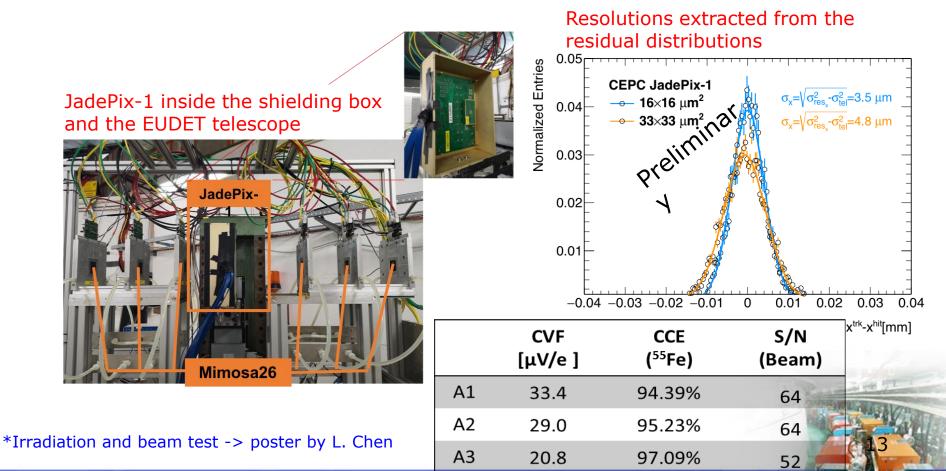

## **DESY Test Beam**

- JadePix-1 position resolution characterized with the EUDET beam telescope and the electron beams at DESY;

- Offline event reconstruction with the EUTelescope software

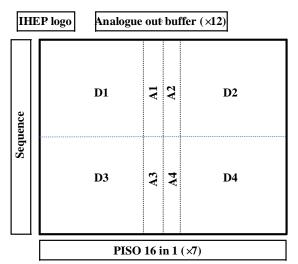

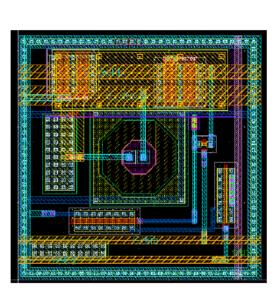

#### Overview of JadePix2 (Team in IHEP)

- Chip area: 3 × 3.3 mm<sup>2</sup>;

- Matrix: 96 × 112 pixels with 8 sub-matrix

- Rolling shutter mode

- Every 16 columns of digital pixel share one

- LVDS transmitter

- 160 MHz clock

- 16-to-1 serializer

- A few columns configured as analog readout

- For calibration of sensing diode

Floorplan of JadePix2

|                                                                      | D1          | A1  | A2    | D2          | D3                | A3     | A4         | D4                  |  |

|----------------------------------------------------------------------|-------------|-----|-------|-------------|-------------------|--------|------------|---------------------|--|

| Diode size                                                           | $4 \mu m^2$ |     |       |             | 8 μm <sup>2</sup> |        |            |                     |  |

| Design Version                                                       | 2: Single-  | end | 1: Di | ifferential | 2: Sing           | le-end | 1: Differe | ntial               |  |

| Matrix size:<br>①48 row×44 col.<br>②48 row×4 col.<br>③48 row×60 col. | 1           | 2   |       | 3           | 1                 | 2      |            | <sup>3)</sup><br>14 |  |

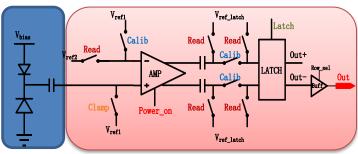

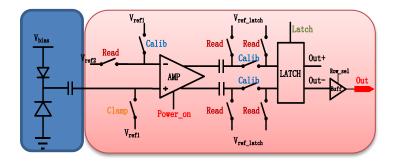

#### JadePix2: Voltage Discrimination in Pixel

- Two versions of Front-end

- Version 1: differential amplifier + dynamic latch

- Version 2: cascaded amplifier (single-ended) + dynamic latch

Version 1: differential amplifier + latch

Version 2: two stage CS amplifiers + latch

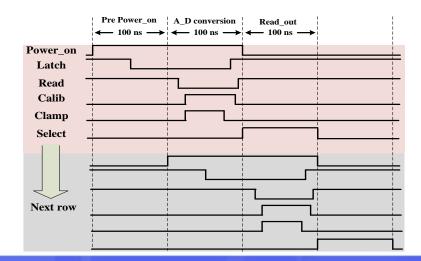

# **Design results of JadePix2**

- Offset cancellation and high precision comparator

- FPN (Fix Pattern Noise) ~ 20 e<sup>-</sup>

- TN (Temporal Noise) ~ 7 e<sup>-</sup>

- Optimal sensing diode selected from JadePix1

- Positively biased

- AC coupled to the amplifier

- Rolling shutter mode

- 100 ns / row (Version 1), 80 ns / row (Version 2)

- 3.7 μA / pixel (Version 1), 6.5 μA / pixel (Version 2)

- Pixel size: 22 × 22 μm<sup>2</sup>

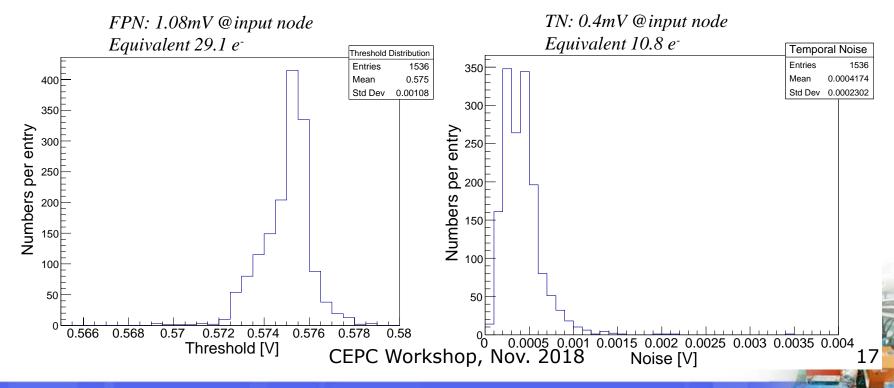

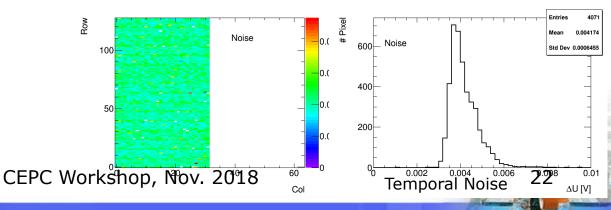

#### **Noise Measurement on JadePix2**

- S-curve measured on Version 1 pixels (differential)

- Scan 'Vref2' while 'Clamp' closed

- ENC = 31 e<sup>-</sup>

- TN ~ 11 e<sup>-</sup>

- FPN ~ 29 e<sup>-</sup>

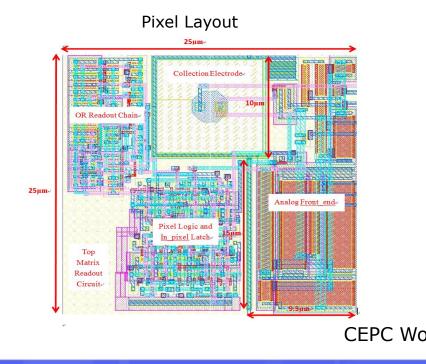

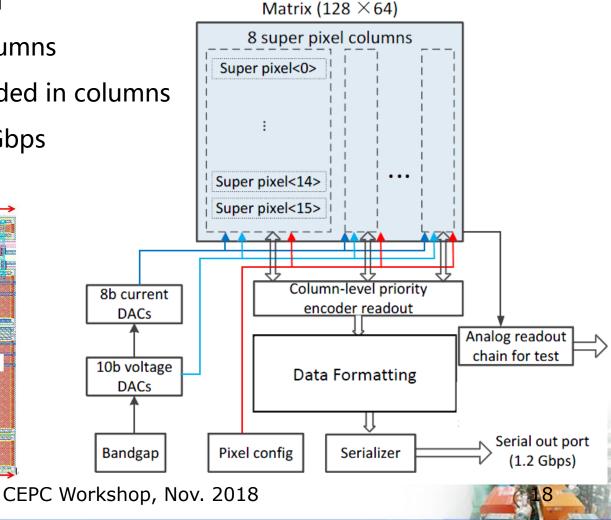

#### Overview of MIC4 (Team in CCNU & IHEP)

- MIC4 (<u>MAPS In CCNU 4</u>)

- Pixel size: 25 um x 25 um

- Matrix: 128 rows x 64 columns

- Zero suppression embedded in columns

- High speed data link 1.2Gbps

Block diagram of MIC4

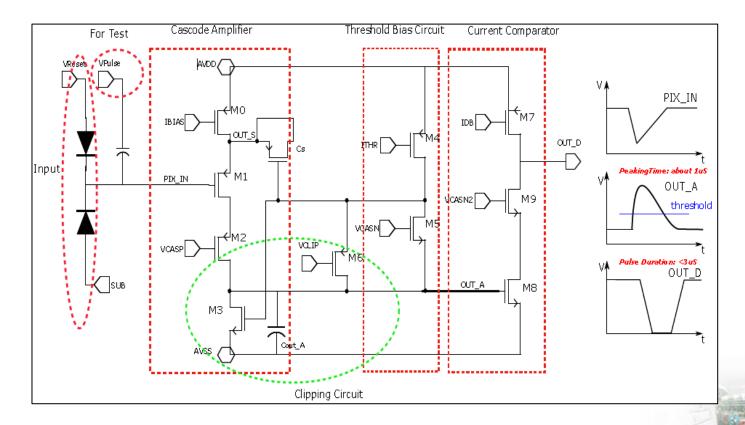

## **MIC4: Pulse Height Discrimination in Pixel**

- Baseline front-end: the same structure as in ALPIDE\*

- \*Reference: G. A. Rinella, NIMA845

- Branch current 61 nA/pixel (increased by a factor of 3)

- Peaking time < 1 μs, duration < 3 μs</li>

### **MIC4: Pulse Height Discrimination in Pixel**

- Alternative front-end: Charge sensitive amplifier + current comparator

- Feedback capacitance 0.2 fF

- Peaking time < 550 ns @ Qin < 1.5 ke<sup>-</sup>

- Pulse duration < 8.3 µs @ Qin < 1.5 ke<sup>-</sup>

- 35 nW / pixel

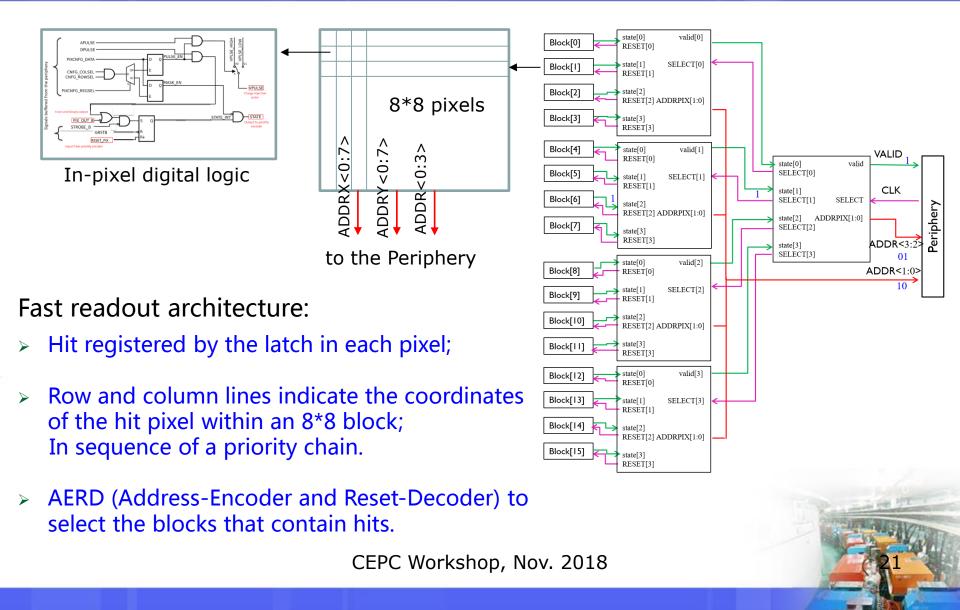

## **Readout Architecture**

## **Noise Measurement on MIC4**

100

50

- A test system has been setup in CCNU

- S-curve measured on pixels with baseline front-end

- Test pulse injection

- Threshold set to 69.8 mV, equivalent to 99 e<sup>-</sup>

- FPN = 21.9 mV, equivalent to 31 ge<sup>-</sup>

- TN = 0.65 mV, equivalent to  $6 e^{-1}$

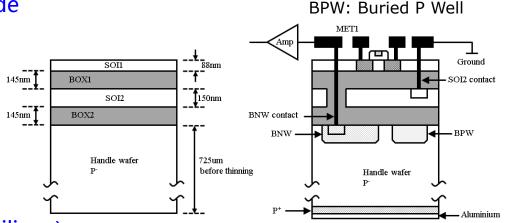

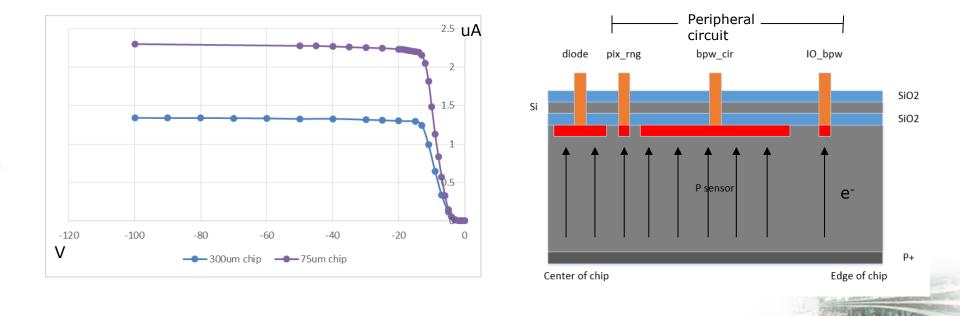

#### Development of SOI Pixel Sensor (Team in IHEP)

- N-in-P sensor capable of full depletion

- BNW and N<sup>+</sup> as collection electrode

- BPW available as P-spray

- Isolation of transistors

- Buried Oxide (insulation)

- SOI2 (grounded for shielding)

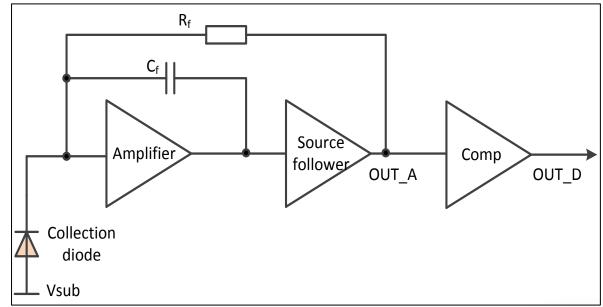

- In-Pixel ampl. & disc:

- Signal charge ~ 4000e (in 50 μm silicon)

- Very small Cd

- Voltage amplifier & comparator

- Very compact pixel ~ 16 μm pitch

BOX: Buried Oxide BNW: Buried N Well

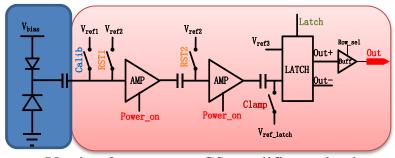

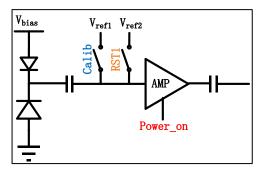

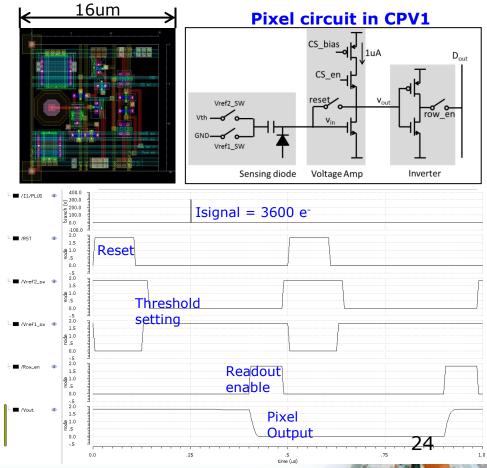

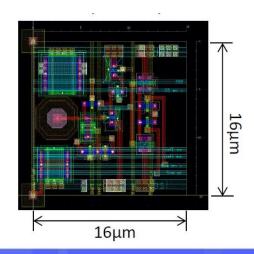

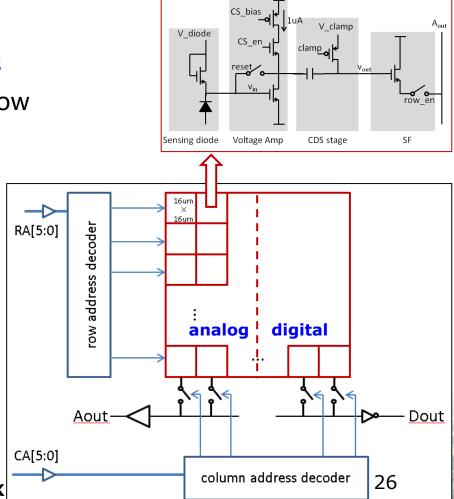

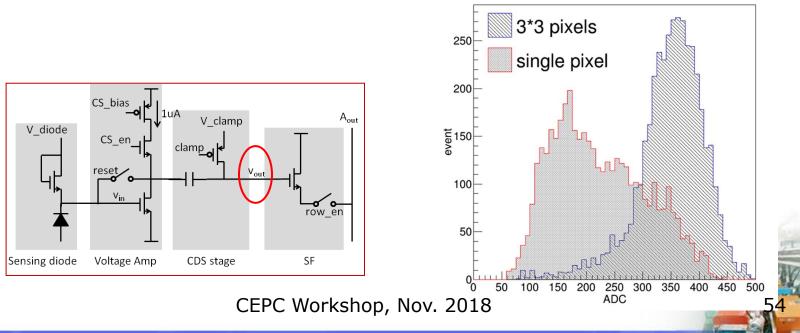

# Pixel design in CPV1

- CPV (<u>Compact Pixel for Vertex</u>)

- Sensing diode, 2 μm

- Cd = 1 fF

- Voltage amplifier, DC Gain ~ 10

- 1 μA, power on when row selected

- Offset cancellation reset

- Inverter as discriminator

- Charge injection at Vin

- Setting threshold

- Minimize layout area

- 16 × 16 μm<sup>2</sup>

#### Simulated Cd @ Vbias = -20 V

| Diode diameter (µm) | 2 | 3   | 4   |

|---------------------|---|-----|-----|

| Cd (fF)             | 1 | 1.8 | 2.8 |

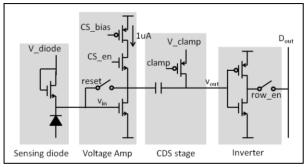

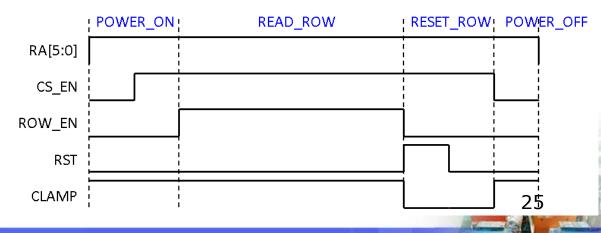

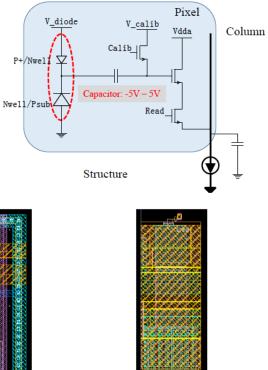

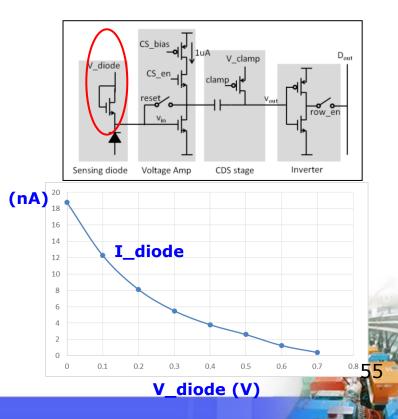

# Pixel design in CPV2

- Pixel circuit adjusted on basis of CPV1

- Discharging transistor added to Vin

- Diode-connected NMOS

- V\_diode = 0V

- Discharging when Vin < 0V</li>

- CDS stage inserted between apmp. and invt.

- Improve RTC and FPN noise

- Setting threshold by V\_clamp

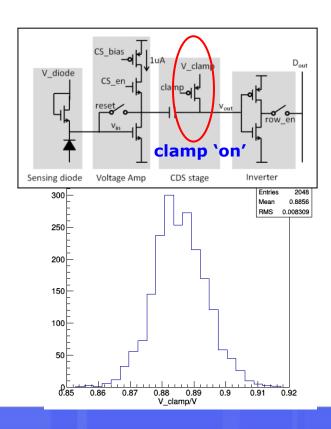

#### **Pixel circuit in CPV2**

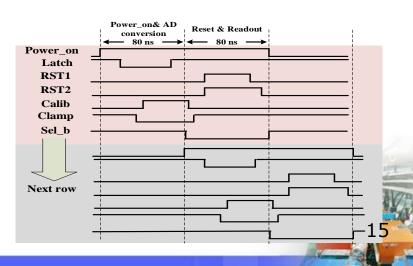

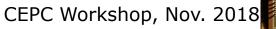

# **Chip architecture**

- Rolling shutter mode

- 100 ns / row

- 64 rows × 64 columns

- Half matrix has SFs in place of inverters

- Address decoder to select column & row

- Very flexible during test

- Same architecture for CPV1/2

- I/O compatible

- Readout using SEABAS\* DAQ system

\*SEABAS: SOI Evaluation Board with Si TCP/IP, by KEK

#### Inverter replaced with a SF

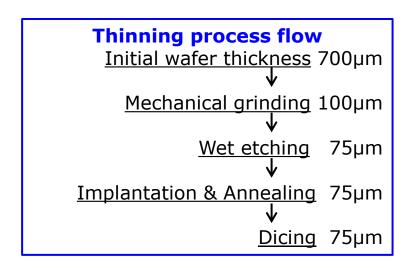

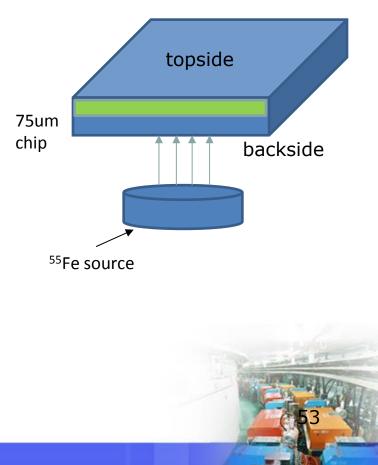

## **Prototype Characterization**

- CPV2 thinned down to 75 μm

- Backside P<sup>+</sup> implantation after thinning

- Very low leakage current

- ~ pA/pixel @ Vbias = -100 V

- Full depletion confirmed with <sup>55</sup>Fe and Infrared laser respectively

- V<sub>depletion</sub> ~ -30 V

- Calibration with <sup>55</sup>Fe 5.9 keV X-ray

- CVF = 123.3 µV/e- @ Vout

- Can be improved by Cascode amplifier

### **Noise Measurement**

- S-curve measured on the digital pixel array

- TN ~ 6 e<sup>-</sup>

300

250

200

150

100

50

0 0

oixel numbers

• FPN ~ 114 e<sup>-</sup>

#### **Digital pixel array S-Curve** 0.8 Normalized response 0.6 0.4 0.2 0\_0.88 0.9 0.92 0.96 0.98 1.02 0.94 1 Vclamp[V] 140 Entries 1991 Entries 1991 0.9704 Mean 120 Mean 0.0007141 RMS 0.01428 RMS 0.0003154 Constant 111.9 100 Constant 330.5 Mean 0.9707 pixel numbers 0.0006986 Mean 80 Sigma 0.01342 Sigma 0.0002894 60 40 20 0.0005 0.001 0.0015 0.002 0.0025 0.003 0.0035 0.004 0.0045 0.005 8.9 0.92 0.94 0.96 0.98 1.02 temporal noise [V] threshold [V]

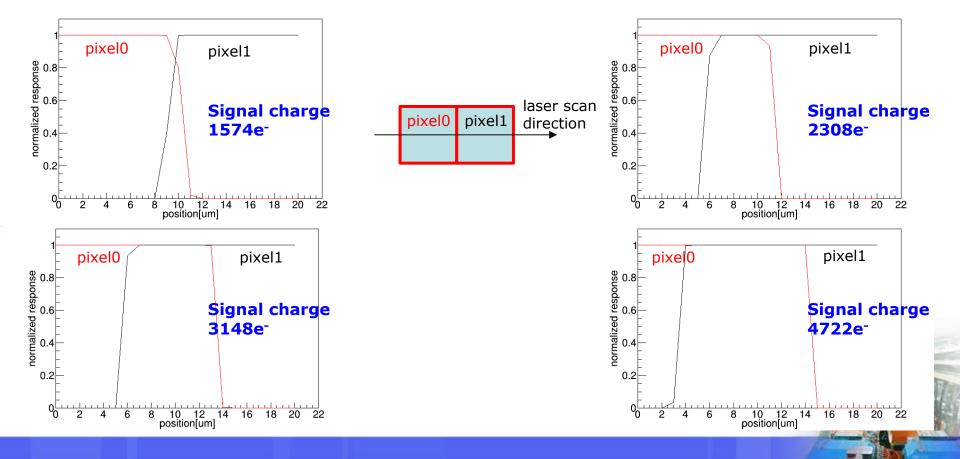

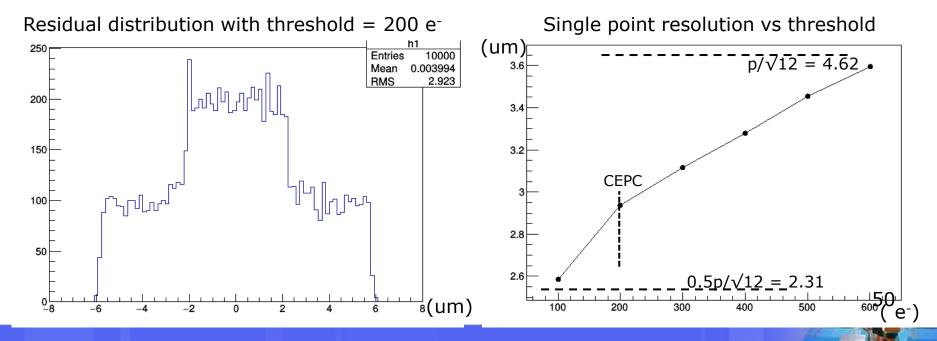

### Laser position scan with different intensity

- Scan across two adjacent digital pixels

- Threshold is fixed (minimum threshold without noise hit)

- Step size of 1µm

- Different beam intensity used

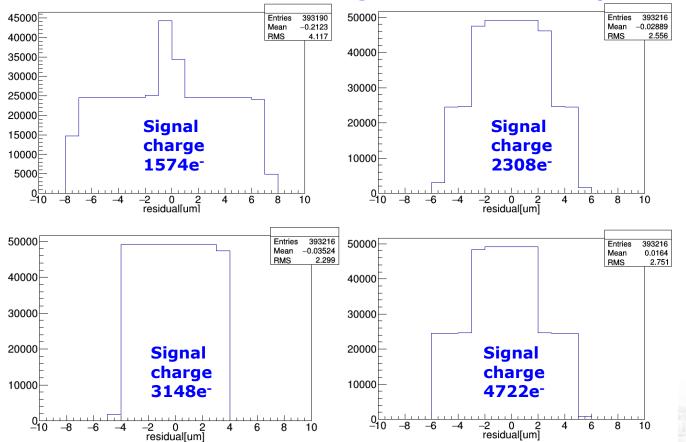

## **Residual distribution**

RMS of residual distribution indicates its single point resolution

**Residual distribution changes with beam intensity**

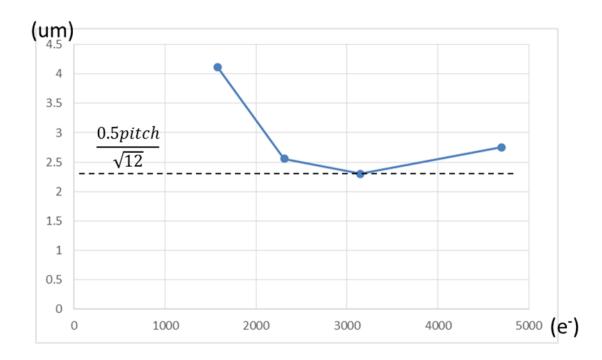

## **Single Point Resolution**

Single point resolution versus signal charge

- Obtained the best resolution of 2.3um around signal charge 3000 e<sup>-</sup>

- Low threshold is critical

## **Comparison of digital pixel chips**

|            | JadePix2    | MIC4        | CPV2                     |

|------------|-------------|-------------|--------------------------|

| Process    | CMOS        | CMOS        | SOI                      |

| Pixel size | 22 × 22 µm² | 25 × 25 µm² | $16 \times 16 \ \mu m^2$ |

| TN (e⁻)    | 11          | 6           | 6                        |

| FPN (e⁻)   | 29          | 31          | 114                      |

#### Development of Pixelated Strip (Team in Shandong University)

- As an alternative technology option for the SIT and FTD

- CMOS pixel sensor is of particular interest

- High granularity

- Low material budget

- Large single chip via stitching

- Possible cost reduction

- Readout channels increased significantly

- Trade off between granularity and readout time needed

- A case study conducted for the CDR writing

| Operation mode                         | H (240) | W (160) | Z (91) |

|----------------------------------------|---------|---------|--------|

| Track multiplicity (BX <sup>-1</sup> ) | 310     | 300     | 32     |

| Bunching spacing (ns)                  | 680     | 210     | 25     |

| SIT-L1 occupancy (%)                   | 0.19    | 0.58    | 0.52   |

| FTD-D1 occupancy (%)                   | 0.17    | 0.54    | 0.48   |

Estimated occupancies of the first layers in the SIT and FTD. Pixel size of  $50 \times 350 \ \mu\text{m}^2$ , readout time of 10  $\ \mu\text{s}$  assumed.

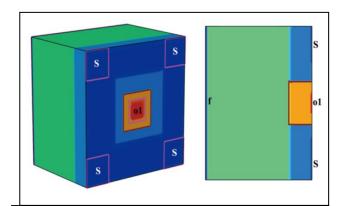

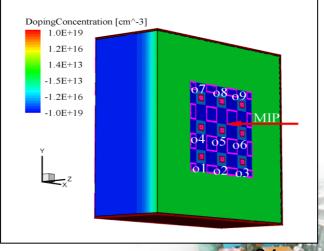

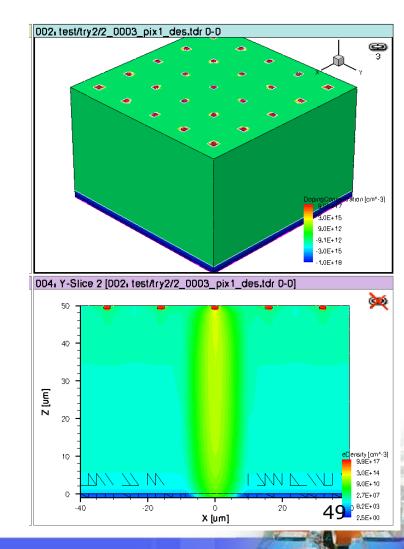

# **TCAD Simulation**

- To understand charge collection in larger pixels is essential for

- Optimal pixel dimensions &

- Diode geometries

- Structures in TCAD simulation

- Pixel size: 21 × 21  $\mu$ m<sup>2</sup>, 21 × 42  $\mu$ m<sup>2</sup>, 21 × 84  $\mu$ m<sup>2</sup>

- A variety of diode geometries

- 1 diode per pixel

- The epitaxial layer: 18  $\mu$ m & 1 k $\Omega$ ·cm

- Bias voltage: 1.8 V

- Hit in the very center of pixel

- 5×5 pixel cluster

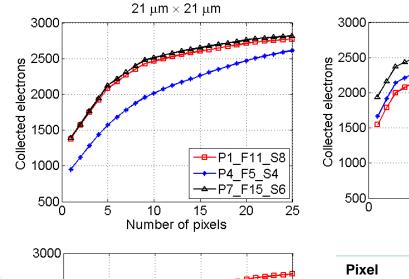

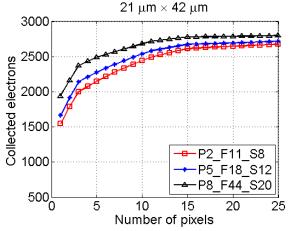

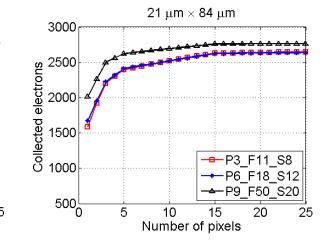

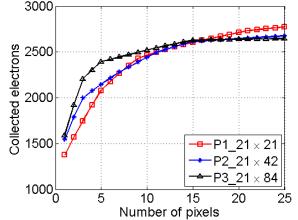

#### **Simulation Results of Charge Collection**

#### • Sum of charge collected by a cluster of 5 × 5 pixels

• Lager pixels exhibit small cluster size

| Pixel                  | <b>P</b> 1 | P2 | <b>P</b> 3 | P4 | P5 | P6 | P7 | P8 | P9 |  |

|------------------------|------------|----|------------|----|----|----|----|----|----|--|

| Pitch(x)(µm)           | 21         | 42 | 84         | 21 | 42 | 84 | 21 | 42 | 84 |  |

| N(D)                   | 1          | 1  | 1          | 1  | 1  | 1  | 1  | 1  | 1  |  |

| F(D)(um <sup>2</sup> ) | 11         | 11 | 11         | 5  | 18 | 18 | 15 | 44 | 50 |  |

| S(D)(um <sup>2</sup> ) | 8          | 8  | 8          | 4  | 12 | 12 | 6  | 20 | 20 |  |

N(D) = number of diodes in each pixel (1)

F(D) = footprint of diode (diode area + pwell opening):

5, 11, 15, 18, 44 & 50 µm<sup>2</sup>

$S(D) = surface of diode: 4, 6, 8, 12 \& 20 \ \mu m^2$

### Prototype Chip using TowerJazz CIS 0.18 μm process

- SUPIX (<u>Shandong University PIX</u>el)

- Total sensitive area: 2 × 7.88 mm<sup>2</sup>

- 9 submatrices corresponding to the pixel

- structures in the TCAD simulation

- Each submatrix: 16 × 64

- Analog readout

- Source follower

- Diode-connected transistor for reset

- Rolling shutter mode

- 32 µs integration time at 2 MHz clock frequency

- 16 parallel analog outputs

- 50 μA current per column

- Gate-enclosed NMOS transistors

- To improve radiation tolerance

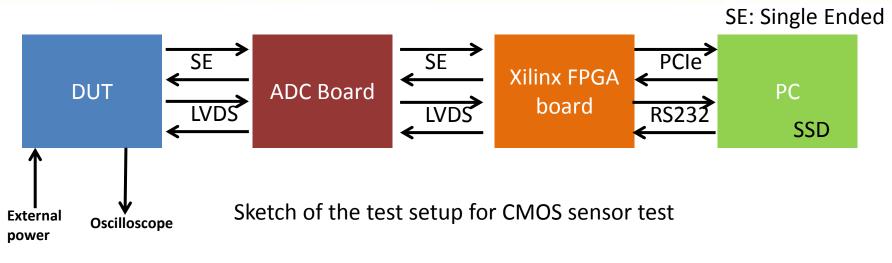

#### Test setup

- The test setup consists of:

- DUT board: customized for the chip

- ADC board: provided by IHEP, the same as used for JadePix1 test

- FPGA board: firmware and DAQ software in development

- SSD high speed data storage  $\rightarrow$  >1Gb/s.

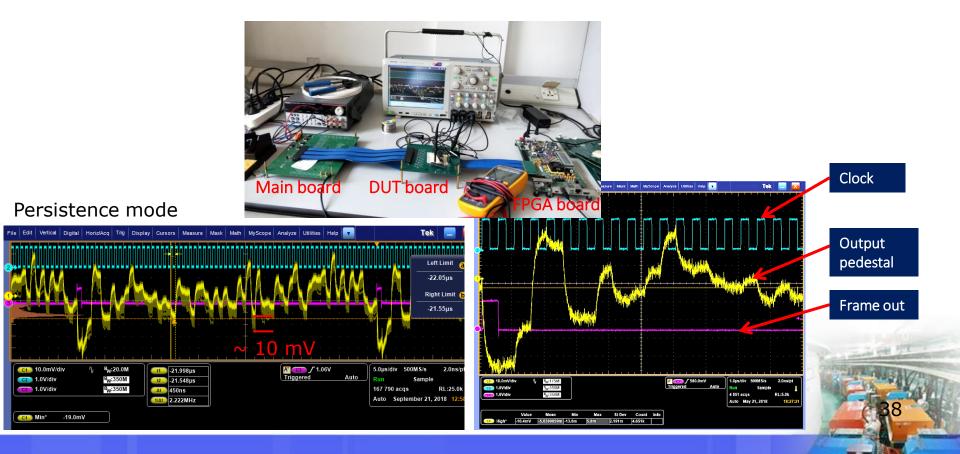

## Test in progress

- Output pedestal observed via oscilloscope

- Variation of baseline measured: 10 mV peak to peak

- <sup>55</sup>Fe source test ongoing

# Summary

- Pixel design of high spatial resolution, low power and fast readout is required for the CEPC silicon tracker.

- A variety of pixel chip designed specifically for CEPC as part of the R&D activities.

- Optimization of sensing diode to improve Q/C

- Low power low noise amplifier and discriminator in pixel

- Fast readout architecture

- Sensing diode Q/C characterized

- Noise of different front-end characterized and compared

- Spatial resolution < 3 μm demonstrated on small pitch of 16 μm

#### **Future Plan on R&D**

- Laboratory and test-beam characterizations

- Coordination of design team for next submission

- Large area chip design

- Radiation hardness

- For time stamp @ Z-pole

- Explore SOI 3D connection technology

- Look for new process with smaller feature size

#### Acknowledgements

- This work is partially supported by the National Nature Science Foundation of China, Grant 11575220.

- And the CAS Center for Excellence in Particle Physics (CCEPP)

#### Thank you for your attention!

Team in IHEP:

L. Chen, J. Dong, R. Kiuchi, X. Lu, Y. Lu, O. Qun, X. Shi, J. Tao, K. Wang, N. Wang, W. Wei, Z. Wu, Y. Zhang , M. Zhao, Y. Zhou , H. Zhu

Team in Shandong University:

J. Dong, L. Li, J. Liu, M. Wang, L. Zhang

Team in CCNU:

C. Gao, W. Ren, X. Sun, D. Wang, L. Xiao, P. Yang

Below are backup slides

#### **CEPC CDR Parameters**

D. Wang

|                                                                      | Higgs           | W             | Z (3T)              | Z (2T)       |  |

|----------------------------------------------------------------------|-----------------|---------------|---------------------|--------------|--|

| Number of IPs                                                        |                 | 2             |                     |              |  |

| Beam energy (GeV)                                                    | 120             | 80            | 45.5                |              |  |

| Circumference (km)                                                   | 100             |               |                     |              |  |

| Synchrotron radiation loss/turn (GeV)                                | 1.73            | 0.34          | 0.036               |              |  |

| Crossing angle at IP (mrad)                                          | $16.5 \times 2$ |               |                     |              |  |

| Piwinski angle                                                       | 2.58            | 7.0           | 23.8                |              |  |

| Number of particles/bunch $N_e$ (10 <sup>10</sup> )                  | 15.0            | 12.0          | 8.0                 |              |  |

| Bunch number (bunch spacing)                                         | 242 (0.68µs)    | 1524 (0.21µs) | 12000 (25ns+10%gap) |              |  |

| Beam current (mA)                                                    | 17.4            | 87.9          | 461.0               |              |  |

| Synchrotron radiation power /beam (MW)                               | 30              | 30            | 16.5                |              |  |

| Bending radius (km)                                                  | 10.7            |               |                     |              |  |

| Momentum compact (10-5)                                              | 1.11            |               |                     |              |  |

| β function at IP $\beta_x^* / \beta_y^*$ (m)                         | 0.36/0.0015     | 0.36/0.0015   | 0.2/0.0015          | 0.2/0.001    |  |

| Emittance $\varepsilon_{\rm r}/\varepsilon_{\rm v}$ (nm)             | 1.21/0.0031     | 0.54/0.0016   | 0.18/0.004          | 0.18/0.0016  |  |

| Beam size at IP $\sigma_{\rm x}/\sigma_{\rm y}$ (µm)                 | 20.9/0.068      | 13.9/0.049    | 6.0/0.078           | 6.0/0.04     |  |

| Beam-beam parameters $\xi_x/\xi_v$                                   | 0.031/0.109     | 0.013/0.106   | 0.0041/0.056        | 0.0041/0.072 |  |

| RF voltage $V_{RF}$ (GV)                                             | 2.17            | 0.47          | 0.10                |              |  |

| RF frequency $f_{RF}$ (MHz) (harmonic)                               | 650 (216816)    |               |                     |              |  |

| Natural bunch length $\sigma_z$ (mm)                                 | 2.72            | 2.98          | 2.42                |              |  |

| Bunch length $\sigma_z$ (mm)                                         | 3.26            | 5.9           | 8.5                 |              |  |

| Betatron tune $v_x/v_y$                                              | 363.10 / 365.22 |               |                     |              |  |

| Synchrotron tune $v_c$                                               | 0.065           | 0.0395        | 0.028               |              |  |

| HOM power/cavity (2 cell) (kw)                                       | 0.54            | 0.75          | 1.94                |              |  |

| Natural energy spread (%)                                            | 0.1             | 0.066         | 0.038               |              |  |

| Energy acceptance requirement (%)                                    | 1.35            | 0.4           | 0.23                |              |  |

| Energy acceptance by RF (%)                                          | 2.06            | 1.47          | 1.7                 |              |  |

| Photon number due to beamstrahlung                                   | 0.29            | 0.35          | 0.55                |              |  |

| Lifetime _simulation (min)                                           | 100             |               |                     |              |  |

| Lifetime (hour)                                                      | 0.67            | 1.4           | 4.0                 | 2.1          |  |

| F (hour glass)                                                       | 0.89            | 0.94          | 0.                  | 99 43        |  |

| Luminosity/IP L (10 <sup>34</sup> cm <sup>-2</sup> s <sup>-1</sup> ) | 2.93            | 10.1          | 16.6                | 32.1         |  |

## **Occupancy at the first Vertex layer**

| Operation mode                                                        | H (240) | W(160) | Z (91) |

|-----------------------------------------------------------------------|---------|--------|--------|

| Hit density (hits $\cdot$ cm <sup>-2</sup> $\cdot$ BX <sup>-1</sup> ) | 2.4     | 2.3    | 0.25   |

| Bunching spacing ( µs)                                                | 0.68    | 0.21   | 0.025  |

| Occupancy (%)                                                         | 0.08    | 0.25   | 0.23   |

Table 4.2: Occupancies of the first vertex detector layer at different machine operation energies: 240 GeV for ZH production, 160 GeV near W-pair threshold and 91 GeV for Z-pole.

Here we assume 10  $\mu$ s of readout time for the silicon pixel sensor and an average cluster size of 9 pixels per hit, where a pixel is taken to be 16×16  $\mu$ m<sup>2</sup>. The resulting maximal occupancy at each machine operation mode is below 1%.

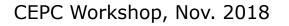

#### **Performance Studies – IP Resolution**

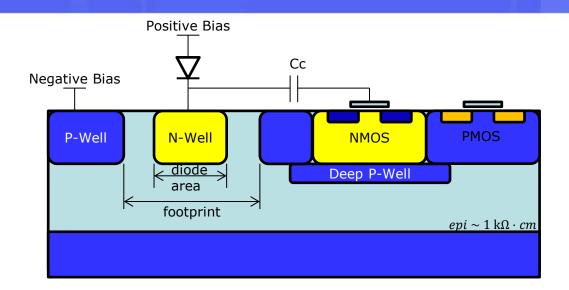

### **Reminder on CMOS Pixel Sensor**

- Diode geometries compete for real estate with transistors

- Diode area: charge collection electrode

- Footprint: spacing between P/N-well is critical for low capacitance

- Methods to apply bias voltage

- Positive bias: AC couple capacitor Cc

- Negative bias: threshold shift of NMOS

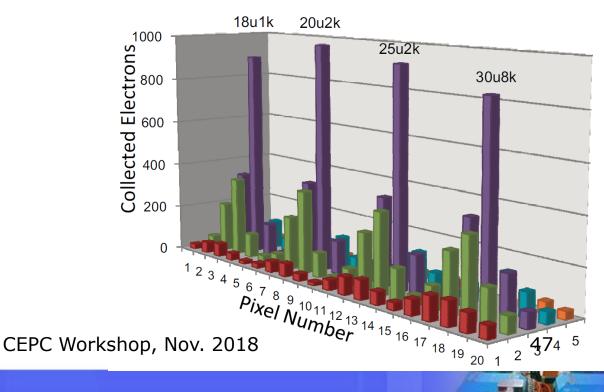

## **Charge Collection in HR epi. layer**

- Pixel cluster with four different epitaxial layers (TCAD simulation)

- 18 μm, 1 kΩ·*cm*

- 20 μm, 2 kΩ·*cm*

- 25 μm, 2 kΩ · cm

- 30 μm, 8 kΩ · cm

#### Seemingly optimal charge collection in 20 $\mu$ m, 2 k $\Omega \cdot cm$

- Maximum peak signal

- Constrained cluster size

### **Positive Bias of Diode**

- Bias voltage up to 10 V

- To measure seed/cluster signal versus V<sub>bias</sub>

- To measure the cluster size

- Optimization of Cc, V\_calib, SF and noise

- Layout

- 16 × 16 µm<sup>2</sup>

- Direct PAD for V\_diode

Pixel Layout

- 16 × 16 μm<sup>2</sup>;

- with transistors under

MIM capacitor

#### Direct PAD layout: for V\_diode

- 250 × 65 μm<sup>2</sup>

- Without ESD

- Both sizes & power lines match with other PADs provided by foundry

### **Device simulation**

#### Device configuration

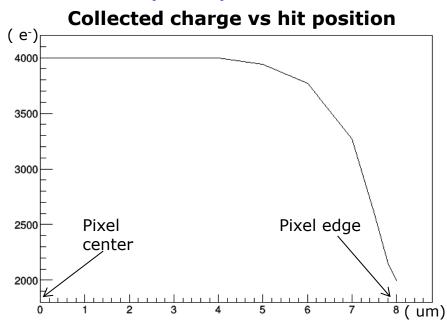

#### How to achieve s.p. resolution < 3um?

- $1 \text{ k}\Omega \cdot \text{cm}$  DSOI wafer (P substrate)

- N<sup>+</sup> electrode 2 μm in diameter

- Pixel pitch 16 μm

- Sensor thickness 50 μm

- Transport of charge carriers

- Analyzed by TCAD tools

### **Device simulation**

Noise smearing and threshold discrimination applied numerically

- ENC ~ 20e-

- Threshold ~ 200e-

- Residual distribution changes with threshold

- Low noise front-end is critical to exploit the charge sharing

- Should note that only perpendicular tracks here

- Detailed study  $\rightarrow$  poster by Z. Wu

# **Thinning process for CPV2**

- Wafer thinning -> Chip dicing

- SOIPIX collaboration

- Thinning to 300 µm is regular

- Thinning to 75 µm is available only on request

- No aluminum on the backside of 75 µm chips

- Enable backside illumination of infrared laser

### Leakage current

- I-V curve @ room temperature

- Total Leakage current reaches the plateau when bias voltage is -15V

- No breakdown up to 100 V

- Diode current is very small both (~nA over the full matrix, 1mm<sup>2</sup>)

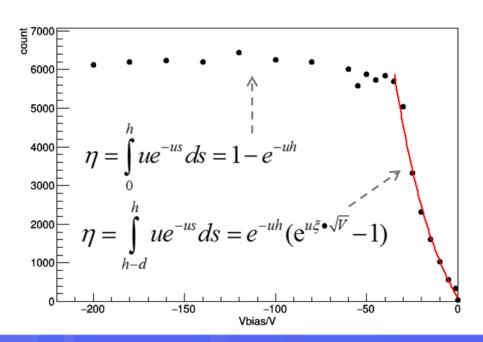

#### **Depletion measurement**

- <sup>55</sup>Fe signal Efficiency versus bias voltage

- X-ray photons counted by analog pixel cluster

- X-ray illuminates the sensor from backside

- Depletion zone develops starting from the topside

- Plateau reached @V<sub>bias</sub> = -30V

#### <sup>55</sup>Fe source calibration

V104

0.8

0.6

0.4

0.2

0.4

0.6

0.8 V\_clamp/V 1.2

1.6

1.4

SFs gain

average: 0.87

- Charge voltage factor (CVF)

- Cluster peak at 360 (ADU)

- SF gain measured 0.87

- CVF = 123.3uV/e<sup>-</sup> @ Vout

- Excessive C<sub>in</sub>?

- 14fF

- Miller capacitance?

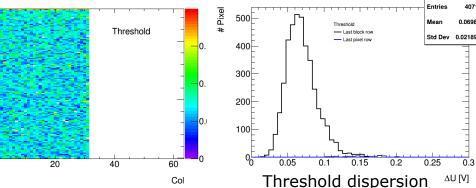

## Investigation of threshold dispersion

- Threshold dispersion 8.3 mV for inverter standalone

- In contrast to 14 mV of complete pixels

- Can be mitigated by improving CVF

- Leakage of NMOS transistor

- Low Vth &

- Very short, W/L = 0.4u/0.2u

- Vin ~ 0.5V, V\_diode = 0.35V

- Minimize integration time

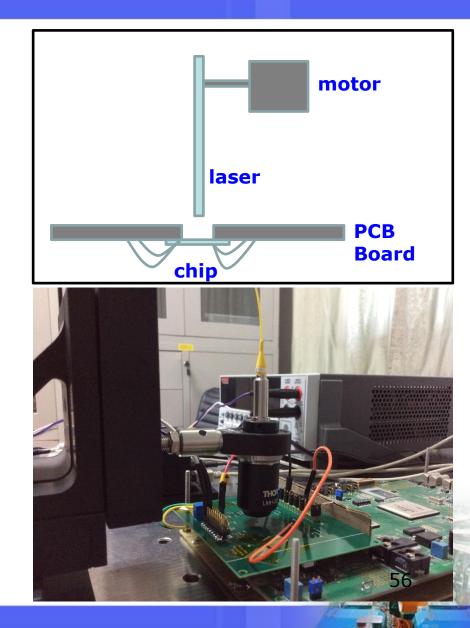

#### Laser test setup

#### 1064nm laser beam

- Focused beam waist ~ 3.4 μm

- Adjustable energy ~ pJ/pulse

- Short pulse duration ~ 100 ps

- 3-dimensional stepping motor

- Minimum step size: 0.1 μm

- Position resolution < 1 μm</li>

- Backside illumination

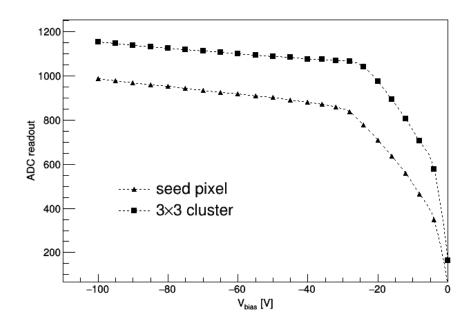

### **Depletion reconfirmed by laser test**

- Laser signal versus bias voltage

- Inflection point @V<sub>bias</sub> = -27V

- Reconfirmed the result of <sup>55</sup>Fe source test

- Choosing  $V_{\text{bias}}$  = -100V in the following laser scan test