# 一种复合信息读出的像素读出芯片及其抗 辐照测试

魏微 樊磊 任佳义 李筱婷 崔珊珊 张杰 王铮 江晓山 朱科军 刘鹏

核探测与核电子学国家重点实验室,北京 中国科学院高能物理研究所

2018-10-16

## 内容

- 项目背景

- 像素芯片设计

- 芯片测试

- 辐照测试

- 总结

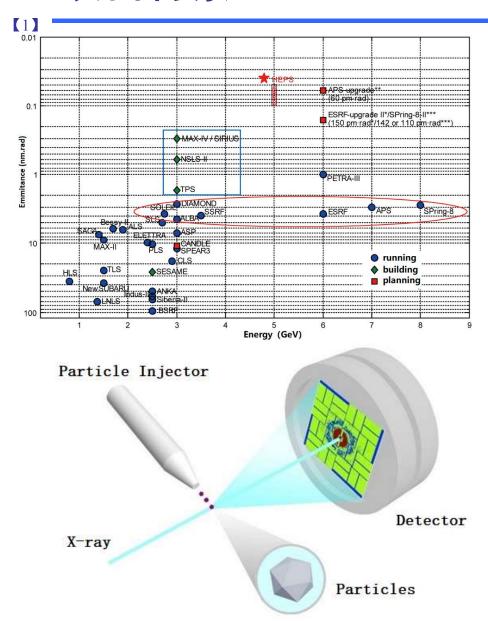

#### 项目背景

- 即将在北京建设的高能同 步辐射光源将实现世界上 亮度最高的光源之一

- 探测器已逐渐成为开展高 质量用户实验的瓶颈之一

- 蛋白质晶体在高亮度辐射 下的衍射实验对探测器提 出了更高的要求:

- 衍射弱

- 对辐射非常敏感

- 为了记录以上动态过程, 传统的单光子计数型像素 探测器已不能满足要求

- 基于帧刷新读出:时间分辨不够

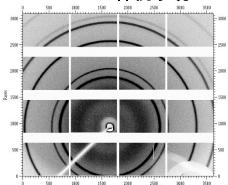

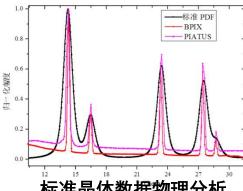

#### 研制基础: 单光子计数型二维硅像素探测器

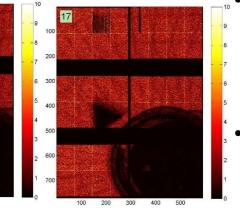

BPIX-1M样机系统

X光标准晶体衍射

X光机成像实验

标准晶体数据物理分析

- 完成了单光子计数模式的二维 硅像素探测器样机的研制

- BPIX-1M样机系统

- 整机包含16个模块, 共约一百万像 素单元

- 灵敏面积: 18cm\*14.4cm, 像素单 元尺寸150µm\* 150µm

- 掌握了探测器设计研制的ASIC、 倒装焊、高速数据读出等全部 关键技术

#### 复合功能像素

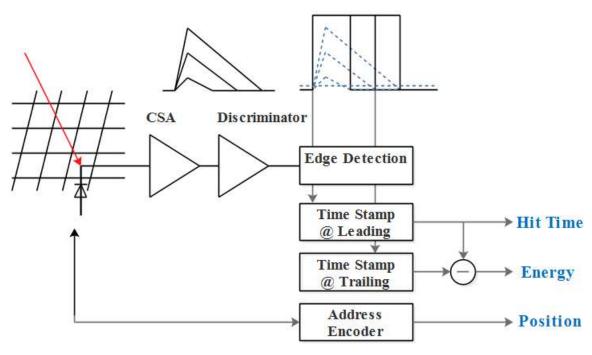

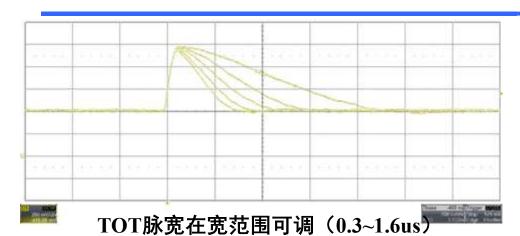

- 基于过阈时间甄别技术,同时获取单光子的时间、 能量信息

- 通过事例驱动型读出结构,实现对高计数率入射事例的连续测量——避免帧刷新过程,提高时间分辨

- 击中位置+时间+能量,实际上实现了对入射粒子的 全信息测量

- 对于稀疏事例,通过事例重建,将可获得连续动态物理过程

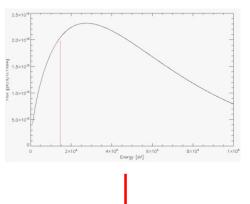

#### 同步辐射单色实验

#### 同步辐射宽带实验

效率提升~104

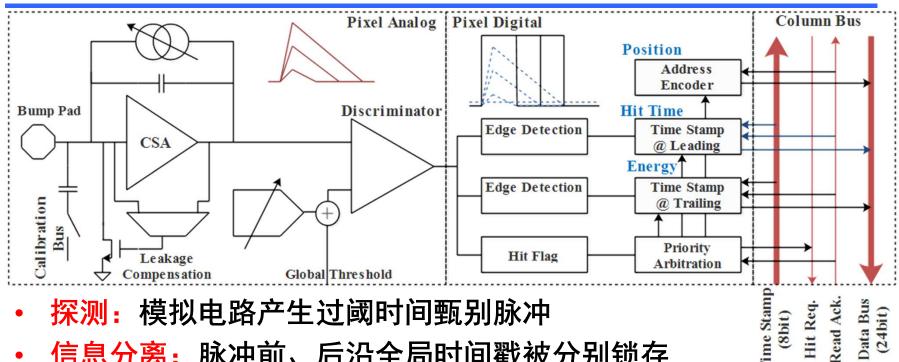

#### 复合功能像素的实现

- 信息分离:脉冲前、后沿全局时间戳被分别锁存

- 前沿时间戳=粒子到达时间

- 后沿时间戳-前沿时间戳=粒子能量

- 像素单元地址编码器ROM=击中位置

- 读出:应对稀疏事例,由帧刷新方式变为事例驱动型读出方式

- 1. 甄别产生击中信息

- 2. 优先级逻辑判断

- 3. 地址编码+TOT时间戳读出至列端FIFO

#### 过阈时间甄别的实现

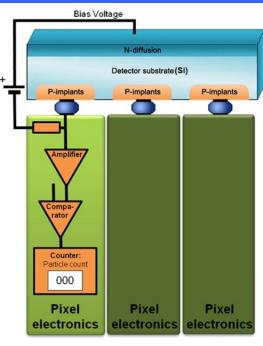

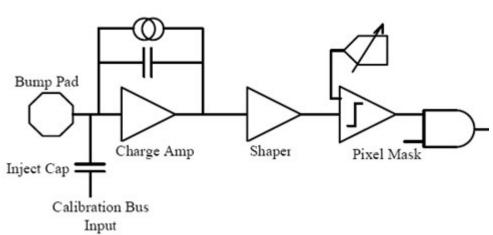

像素单元电路——模拟电路框图

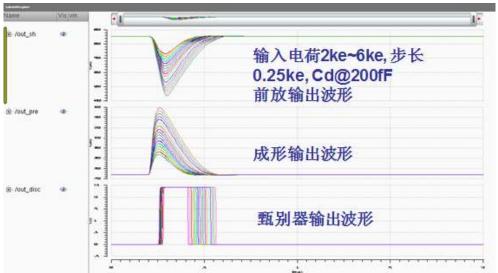

输入信号与过阈时间甄别变换的仿真波形

- · 在单光子计数型像素探测器样机BPIX中[2],已经完成了过阈时间甄别模拟单元电路的设计与验证

- 基于电荷灵敏前放和甄别

- 过阈时间变换的实现:

- CSA:基于线性放电反馈, 产生底宽与幅度(能量) 成正比的三角波

- 甄别器:前沿甄别将三角 波转换为数字脉冲

- 辅助模块:

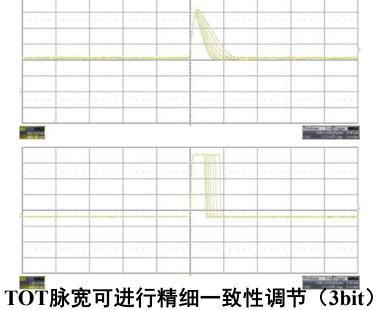

- 阈值一致性调节

- 放电速率一致性调节

- 刻度、像素使能

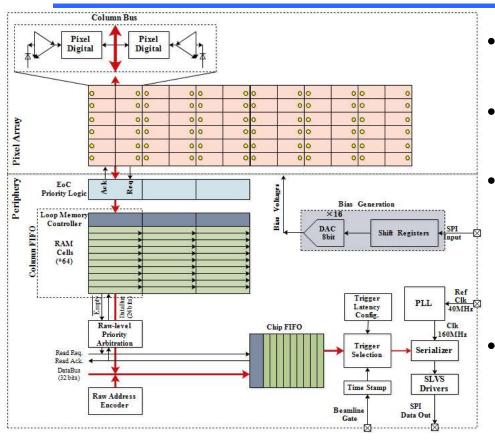

#### 芯片整体结构——事例驱动型读出

- 针对同步辐射门控实验的要求,基于 触发符合方式进行了兼容性设计

- Trigger Window读出/ Triggerless

- 外围功能区还包含了片上参考源、偏置产生、波形监控、慢控制配置等

- 实现了芯片全数字控制与全数字输出

- · 芯片由像素阵列灵敏区和外围电路 功能区组成

- 事例驱动型数据读出基于优先级仲 裁+二级缓存结构

- 列端逻辑功能(一级缓存)

- 优先级逻辑:处理各列像素击中信息,产生应答信号

- 列端FIFO:将随机信息进行一级缓存,等待芯片全局读出(解随机)

- 芯片全局逻辑(二级缓存)

- 全局优先级逻辑:简化版的像素级 优先级逻辑,对各列FIFO缓存信息 进行优先级读出

- 全局FIFO: 匹配数据源与读出接口 速率

- 高速串行接口

- 32bits/hit, PLL+Serializer+SLVS接口, 与FPGA通讯

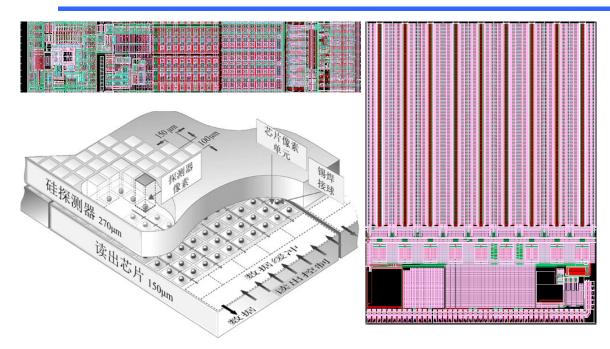

#### 芯片设计

| 指标     | 数值                         | 指标     | 数值            |

|--------|----------------------------|--------|---------------|

| 单元尺寸   | $50\times250\mu\text{m}^2$ | 通道数    | 18列×60行(1080) |

| 输入方式   | 负电荷直流耦合                    | 输入电容   | 100~500fF     |

| 等效噪声电荷 | 200e-                      | 平均功耗   | 50μW/pixel    |

| 模数变换方式 | 过阈时间变换                     | 电荷分辨率  | 4bit          |

| 平均计数率  | 200MHz/cm <sup>2</sup>     | 读出时钟频率 | 40MHz         |

| 读出方式   | LVDS串行读出                   | 抗辐照总剂量 | 50Mrad        |

- 基于CMOS 130nm 1P8M 工艺设计

- · 完成了基于MPW的全功 能芯片设计

- 像素单元尺寸 50×250μm²

- 原型芯片包含18×60像 素(1080通道)

- 面积4.5×4.5mm<sup>2</sup>

- · 将通过工程批流片实现 全尺寸芯片,继而通过 倒装焊与Sensor实现互联 ,完成探测模组的设计

- 相关技术已在BPIX样 机中实现了工程验证

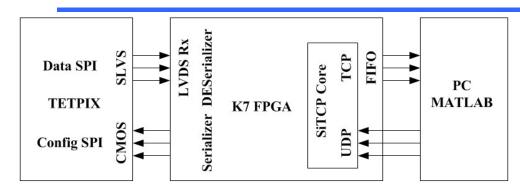

#### 芯片测试读出系统

- · 数据交互:基于KC705开发板设计

- 读出:芯片高速SPI→FPGA解串打包缓存→ 基于SiTCP的TCP/IP协议读出至PC

- 配置: PC基于SiTCP的UDP协议下发→FPGA 整合→慢速SPI配置

- PC数据界面:基于MATLAB脚本

- 可以在单一平台上实现对产生器的控制和对芯 片数据的读出,避免了在Labview等多个软件 环境中的频繁切换

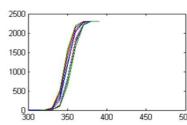

- 实现了对多像素的自动测试与数据接收,并通过刻度算法生成刻度表

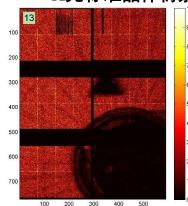

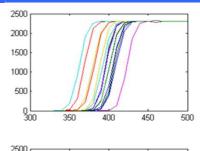

## 芯片主要性能测试

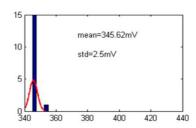

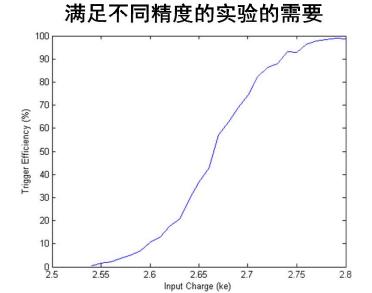

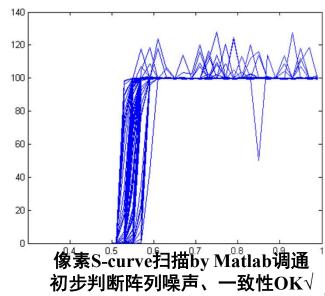

Scurve by 数字读出 ENC ~50e- (未能量刻度)

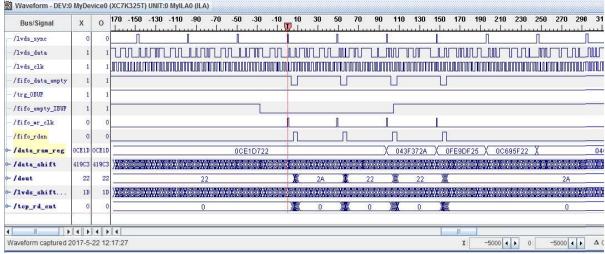

#### 芯片整体读出测试

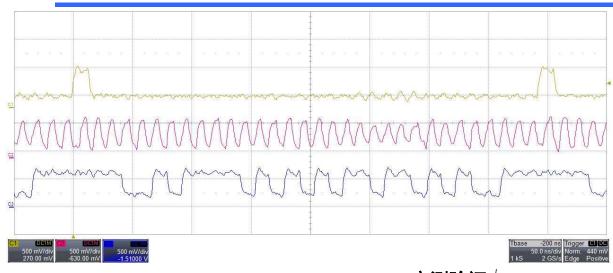

SLVS SPI-interface @ 160Mbps, 实测验证√

多像素同时击中,事例驱动+Hit buffer流水线读出, 32bits/event@SPI, 实测验证√

- · 高速串行接口功能正常

- 通过ChipScope观测多 像素同时击中逻辑及输 出正常

- · 完成了阵列一致性刻度 的Firmware编写,表 明像素阵列整体工作正 常,不一致性在合理范 围

• 抗辐照敏感——删除此页

#### 性能总结

| 设计指标   | 数值                         | 实测指标                       |

|--------|----------------------------|----------------------------|

| 单元尺寸   | $50\times250\mu\text{m}^2$ | $50\times250\mu\text{m}^2$ |

| 通道数    | 18列×60行(1080)              | 18列×60行                    |

| 输入电容   | 100~500fF                  | 80~200fF                   |

| 等效噪声电荷 | 200e-                      | 40~120e-                   |

| 模数变换方式 | 过阈时间变换                     | 过阈时间变换                     |

| 平均功耗   | 50μW/pixel                 | 38µW/pixel                 |

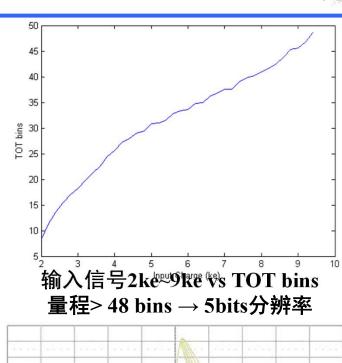

| 电荷分辨率  | 4bit                       | 5bit                       |

| 平均计数率  | 200MHz/cm <sup>2</sup>     | > 200MHz/cm <sup>2</sup>   |

| 读出方式   | LVDS串行读出                   | SLVS SPI                   |

| 读出时钟频率 | 40MHz                      | 160MHz                     |

|        |                            |                            |

- 通过对芯片的全面测试表明,目前芯片各项指标已初步满足项目各项 需求

- 芯片还实现了引脚单侧排布和三边可拼接的接口设计,具备未来模块 化扩展的条件

# Thank you!

本项目得到了基金重点课题(No. 11235013)以及科技部重点研发计划(No. 2016YFA0401300)的支持

特别感谢美国SMU大学叶竞波教授团队对芯片辐照测试工作的帮助