### **Status of Digital Pixel**

Tianya Wu CEPC MOST2 Chips Meeting <u>twu@ifae.es</u> 14-08-2018

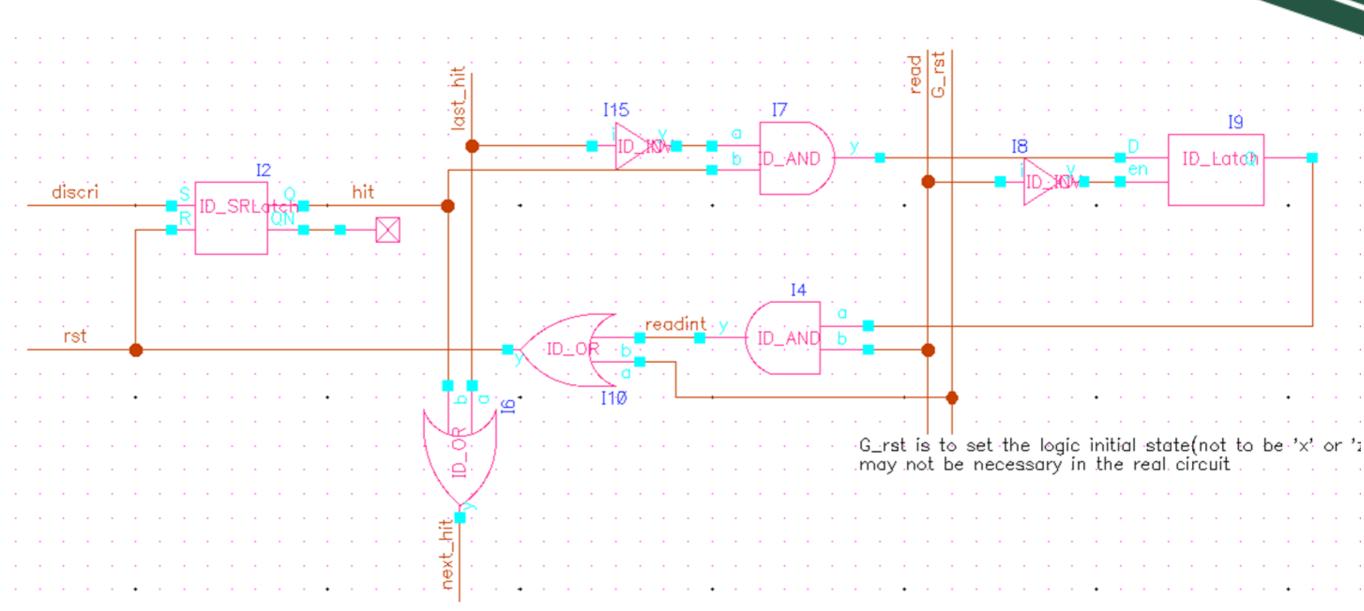

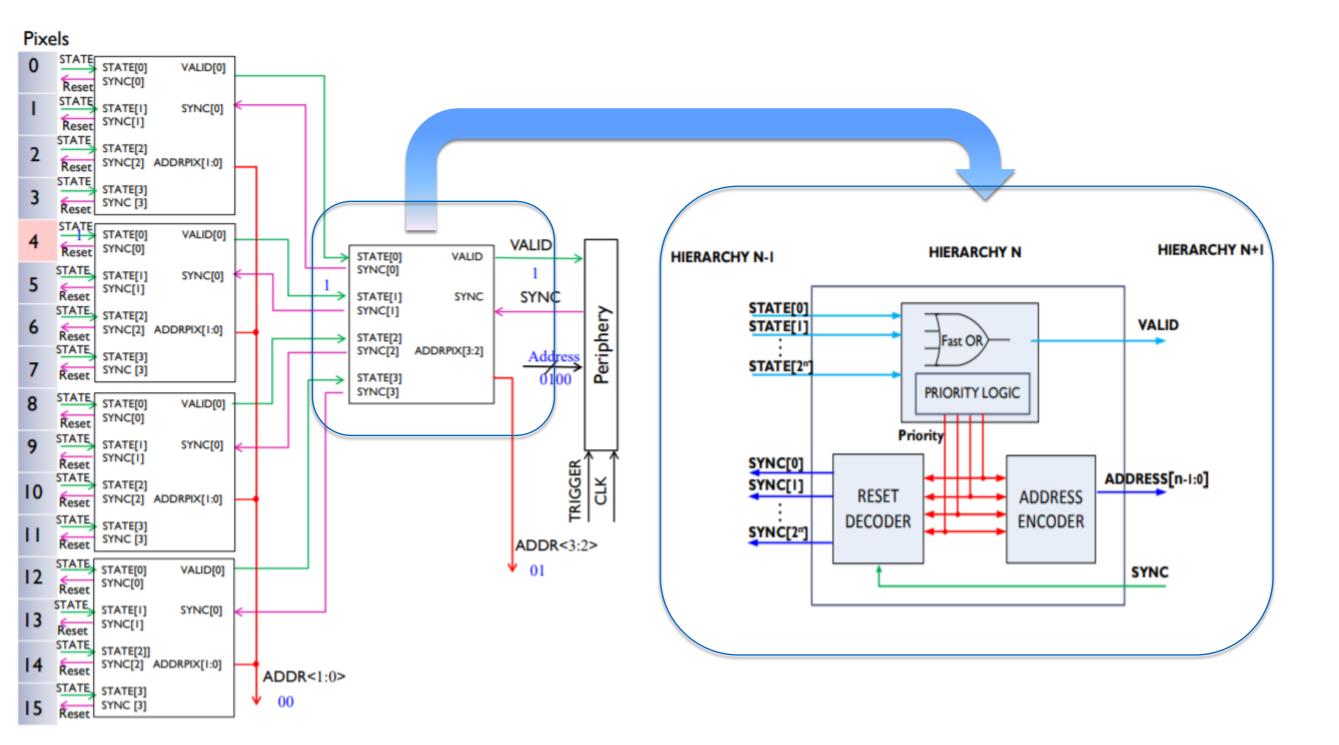

#### Logic scheme of Digital Pixel

2

CENTRAL CHINA NORMAL UNIVERSITY

3.3

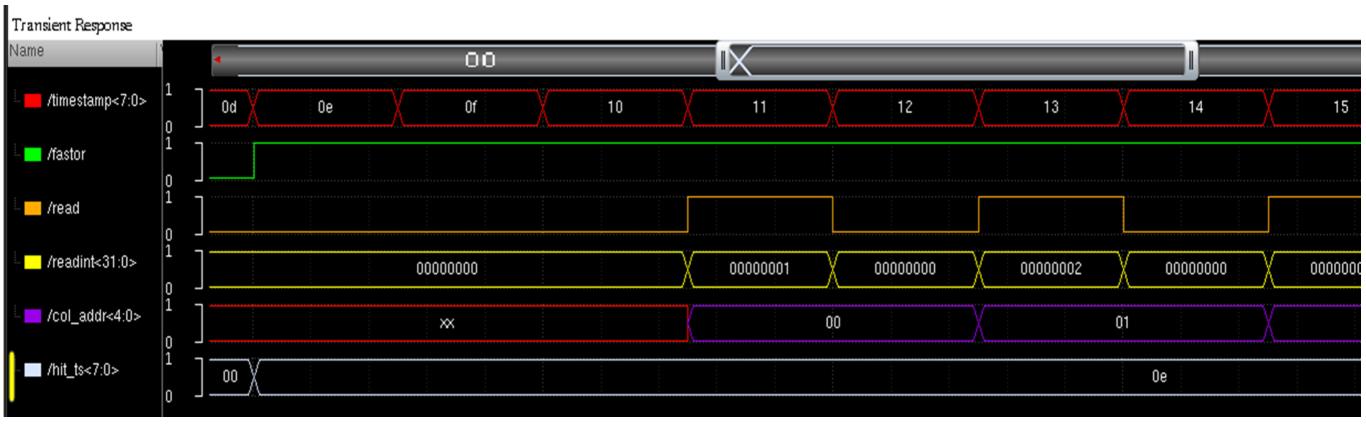

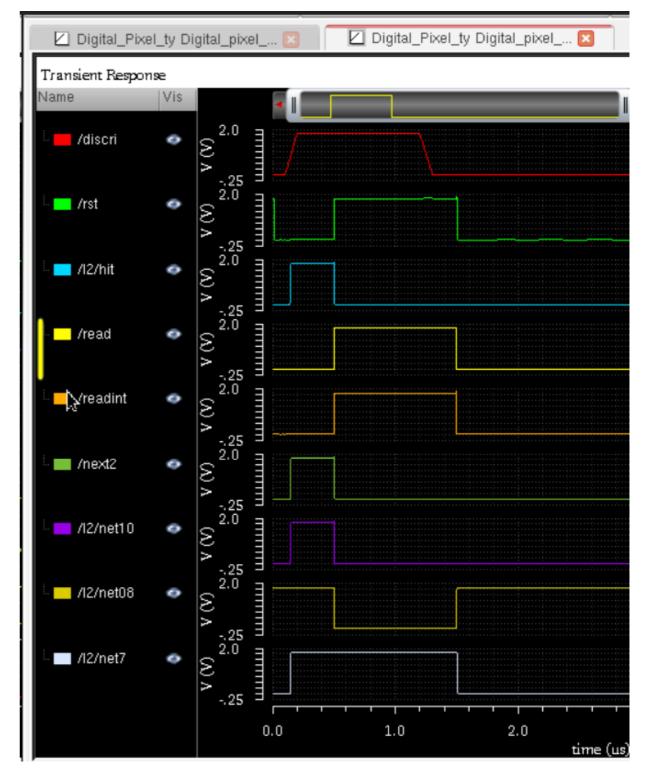

# • From the waveform of simulation, we can see that this logic structure works fine.

3

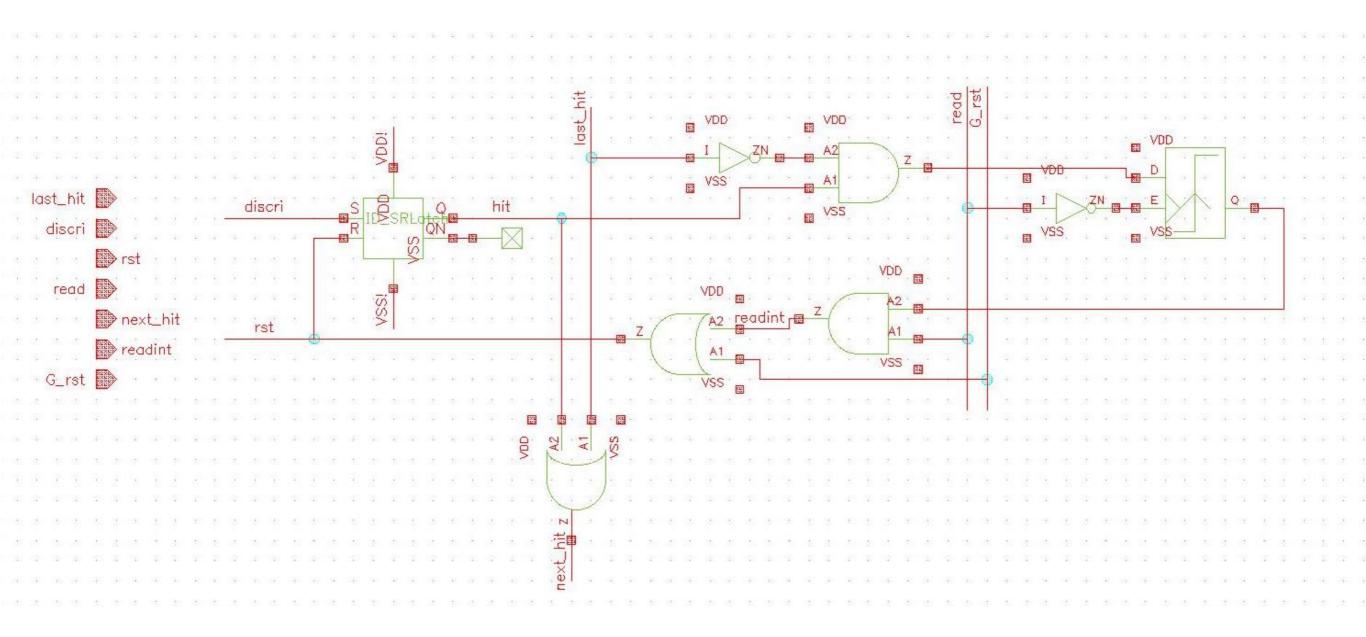

### I exchanged all the logic gates from TowerJazz digital library. Everything seems fine, but I can't simulate it with pure Verilog blocks correctly.

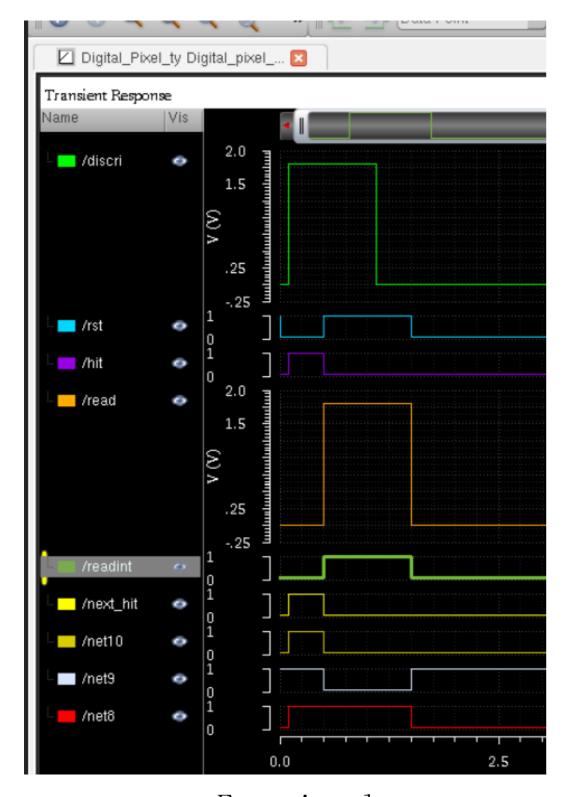

### **Simulation result**:

the real circuit output is the same with functional one.

### Real circuit simulation output

### Functional simulation output

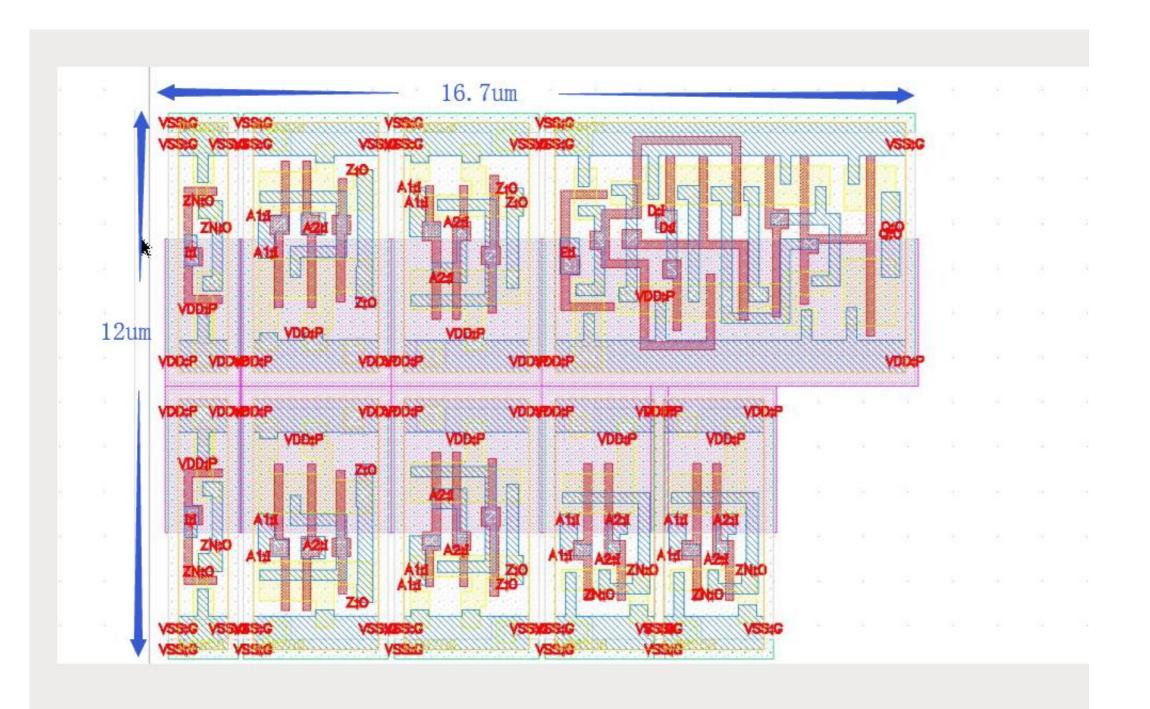

First layout of every single gate without any wires. I think it can be smaller but won't be too much.

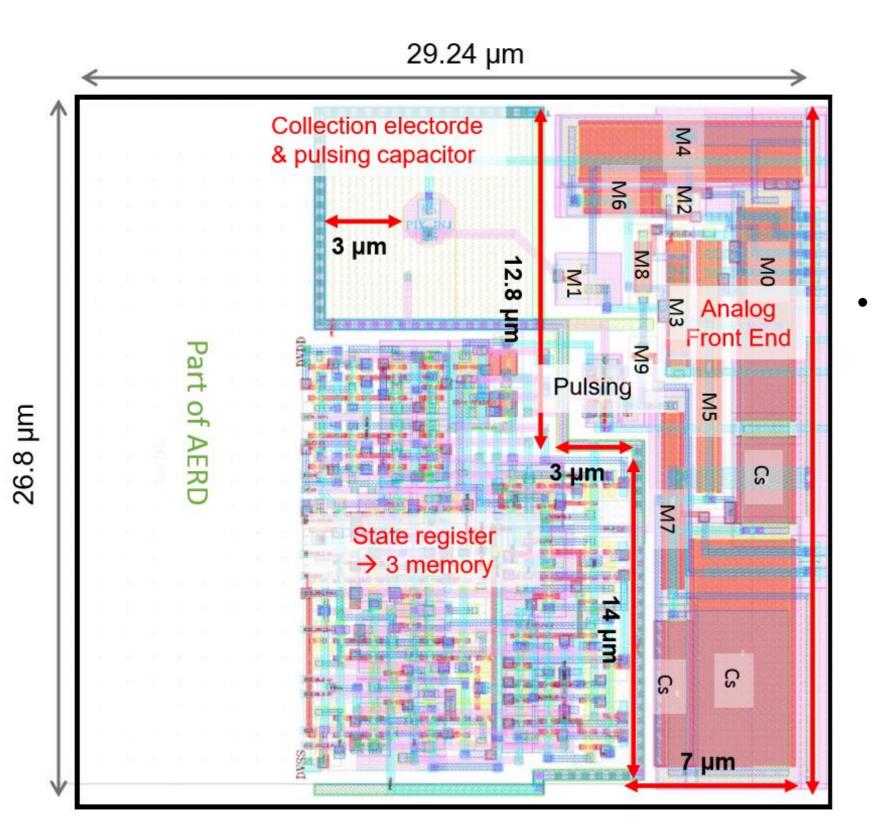

#### Layout on ALPIDE

If the analog front end is the same with ALPIDE, that means digital part should be within 13x19 um

#### The decode scheme and basic block structure of ALPIDE

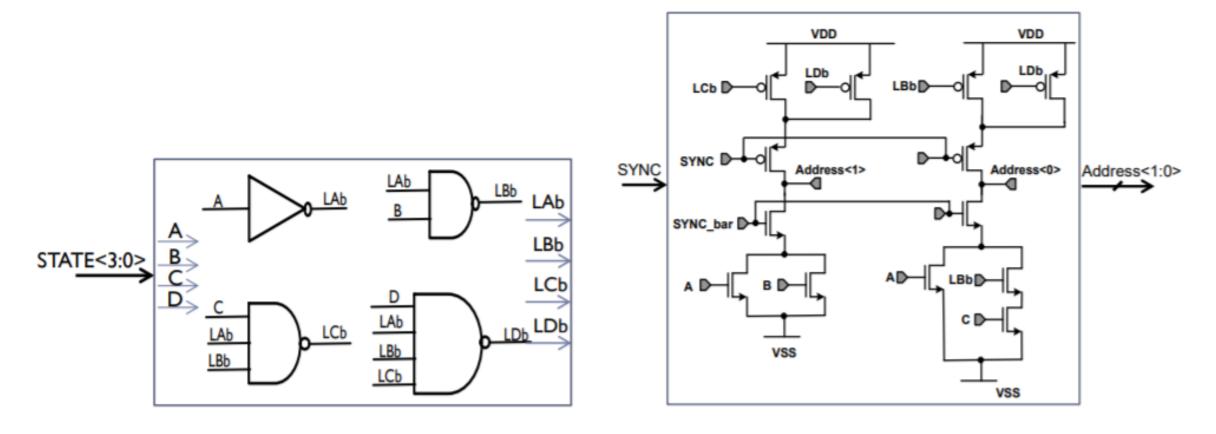

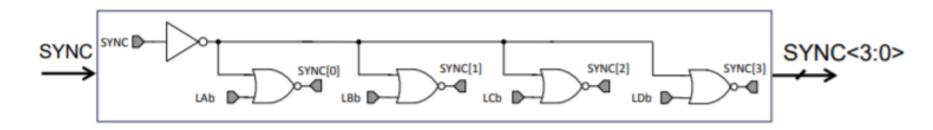

#### The implemented circuit of the basic block of ALPIDE

(a) priority logic of four inputs.

(b) combinatorial address encoder logic.

(c) reset decoder logic.

## Thanks for your attention.