# Vertex Tracker Detector

<u>Qun Ouyang</u>(IHEP), Xiangming Sun(CCNU), Meng Wang(SDU) On behalf of the study group

September 13-15, 2018 Beijing

CEPC Physics and Detector CDR International Review

# **Outline**:

- Requirements and challenges

- Baseline design and performance studies

- Sensor technology options

- Mechanics and Integration

- R&D activities

- Summary

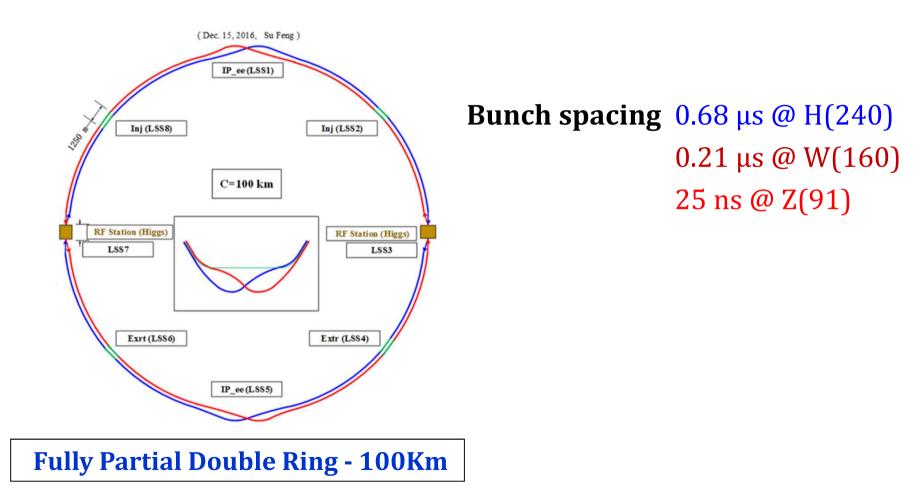

### **Reminder: CEPC Beam Timing**

Circular e<sup>+</sup>e<sup>-</sup> Higgs (Z) factory two detectors, 1M ZH events in 10yrs E<sub>cm</sub>≈240GeV, luminosity ~2×10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>, (1.6×10<sup>35</sup> cm<sup>-2</sup>s<sup>-1</sup> at the Z-pole)

#### **Vertex Detector Requirements**

- Efficient tagging of heavy quarks (b/c) and  $\tau$  leptons

- $\longrightarrow$  impact parameter resolution

$$\sigma_{r\phi} = 5 \oplus \frac{10}{p(GeV)\sin^{3/2}\theta} (\mu m)$$

- Detector system requirements:

- $-\sigma_{\rm SP}$  near the interaction point:  $<3 \,\mu m \longrightarrow \sim 16 \,\mu m$  pixel pitch

- material budget:  $\leq 0.15\% X_0/layer$

- first layer located at a radius: ~1.6 cm

- pixel occupancy:  $\leq 1\%$

- power consumption  $< 50 \text{mW/cm}^2$ , if air cooling used

- $\sim \mu s$  level readout

- \* Radiation tolerance: see slide 8 \* Time stamp: needed for short bunch spacing

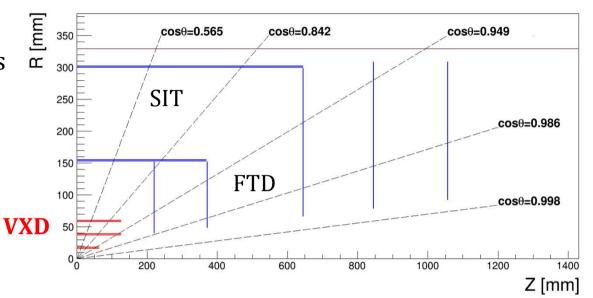

### **Baseline Vertex Detector Layout**

#### <u>VXD</u>: B=3T

- 3 layers of double-sided pixels

- $\sigma_{SP}$ =2.8µm in L1

- Faster pixel sensor in L2, to provide time-stamp

- Polar angle  $\theta \sim 15$  degrees

| spatial resolution  |         | R (mm) | z  (mm) | cos 0 | σ <sub>sp</sub> (μm) |

|---------------------|---------|--------|---------|-------|----------------------|

| -<br>VXD parameters | Layer 1 | 16     | 62.5    | 0.97  | 2.8                  |

|                     | Layer 2 | 18     | 62.5    | 0.96  | 6                    |

|                     | Layer 3 | 37     | 125.0   | 0.96  | 4                    |

|                     | Layer 4 | 39     | 125.0   | 0.95  | 4                    |

|                     | Layer 5 | 58     | 125.0   | 0.91  | 4                    |

| -                   | Layer 6 | 60     | 125.0   | 0.90  | 4                    |

Sept 13-15, 2018 CEPC physics and detector CDR international review

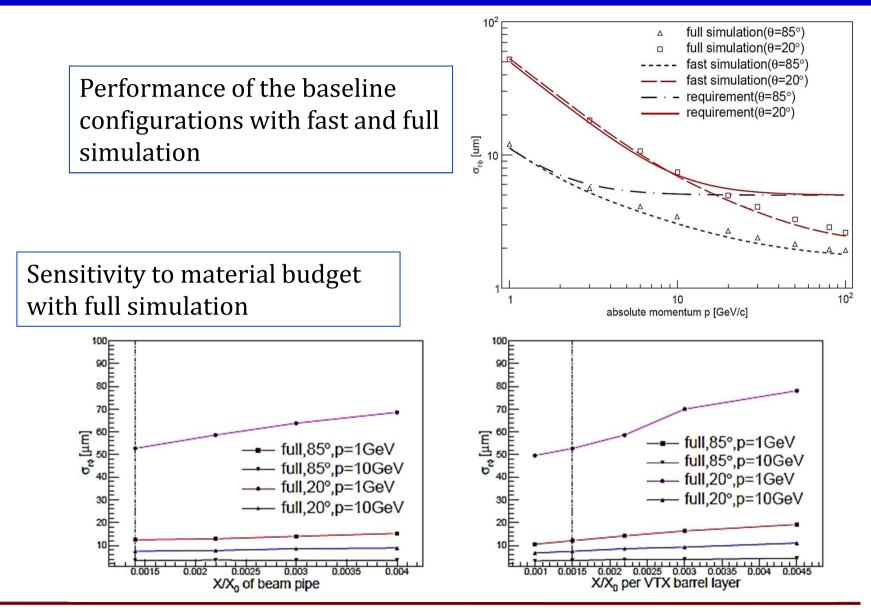

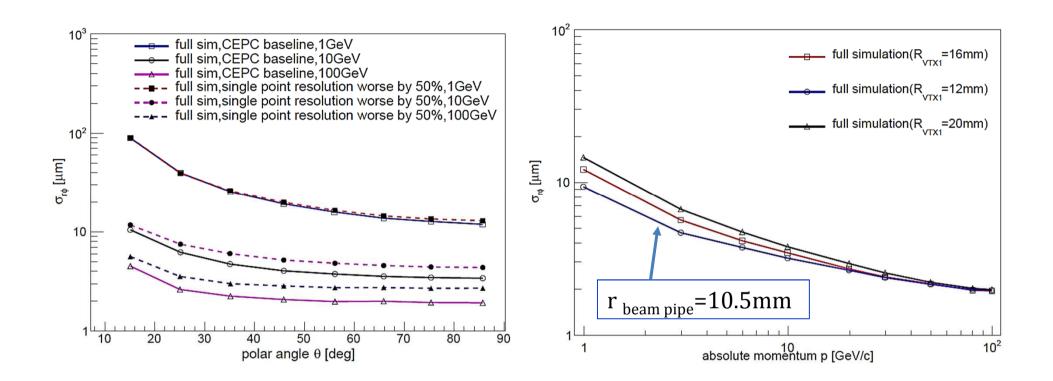

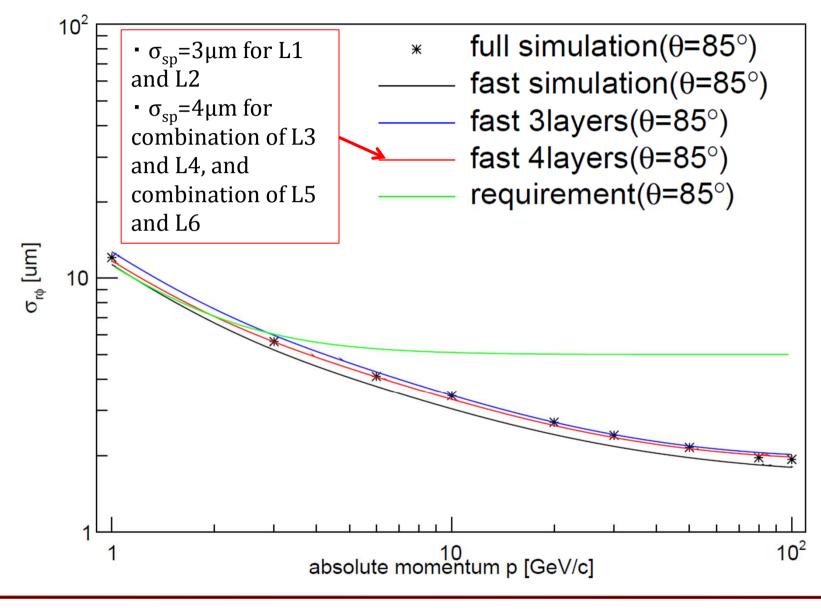

### **Performance Studies – IP Resolution**

CEPC physics and detector CDR international review

#### **Performance Studies – IP Resolution**

Sensitivity to single-point resolution and innermost radius with full simulation

### **Beam-Induced Radiation Backgrounds**

|                                                         | H (240) | W (160) | Z (91)   |

|---------------------------------------------------------|---------|---------|----------|

| Hit Density [hits/cm <sup>2</sup> ·BX]                  | 2.4     | 2.3     | 0.25     |

| TID [MRad/year]                                         | 0.93    | 2.9     | 3.4 - 62 |

| NIEL [ $10^{12}$ 1 MeV $n_{eq}$ /cm <sup>2</sup> ·year] | 2.1     | 5.5     | 6.2      |

**Table 9.4:** Summary of hit density, total ionizing dose (TID) and non-ionizing energy loss (NIEL) with combined contributions from pair production and off-energy beam particles, at the first vertex detector layer (r = 1.6 cm) at different machine operation energies of  $\sqrt{s} = 240$ , 160 and 91 GeV, respectively.

|                                                                       | H(240) | W(160) | Z(91) |

|-----------------------------------------------------------------------|--------|--------|-------|

| Hit density (hits $\cdot$ cm <sup>-2</sup> $\cdot$ BX <sup>-1</sup> ) | 2.4    | 2.3    | 0.25  |

| Bunching spacing ( µs)                                                | 0.68   | 0.21   | 0.025 |

| Occupancy (%)                                                         | 0.08   | 0.25   | 0.23  |

**Table 4.2:** Occupancies of the first vertex detector layer at different machine operation energies: 240 GeV for ZH production, 160 GeV near W-pair threshold and 91 GeV for Z-pole.

detector occupancy <1%, assuming 10  $\mu$ s of readout time for the silicon pixel sensor and an average cluster size of 9 pixels per hit.

### **Sensor Technology Options**

| Technology                               | Examples                                 | Small<br>pixels | Low<br>mass | Low<br>power | Fast<br>timing |

|------------------------------------------|------------------------------------------|-----------------|-------------|--------------|----------------|

| Monolithic CMOS MAPS                     | Mimosa CPS                               | ++              | ++          | ++           | -              |

| Integrated sensor/amplif. + separate r/o | DEPFET, FPCCD                            | +/++            | 0           | +            | -              |

| Monolithic CMOS with depletion           | HV-CMOS, HR-CMOS                         | +               | ++          | 0            | +              |

| 3D integrated                            | Tezzaron, SOI                            | ++              | +           | 0            | ++             |

| Hybrid                                   | CLICpix+planar sensor,<br>HV-CMOS hybrid | +               | 0           | +            | ++             |

Ref: Recent developments in LC vertex and tracking R&D, Dominik Dannheim, LCWS 2015

Many technologies from ILC/CLIC could be referred. BUT, unlike the ILD/CLIC, the CEPC detector will operate in continuous mode.  $\rightarrow$  without power-pulsing

### **Sensor Technology Options**

#### **Possible technologies for CEPC vertex**

- HR-CMOS sensor with a novel readout structure (ALPIDE @ ALICE-ITS upgrade)

- relatively mature technology

- <50mW/cm<sup>2</sup> expected

- Capable of readout every  ${\sim}4\mu s$

- **SOI** sensor with similar readout structure

- Fully depleted HR substrate, potential of  $16 \mu m$  pixel size design

- Full CMOS circuit

- **DEPFET**: possible application for inner most vertex layer

- small material budget, low power consumption in sensitive area

- **3D-IC**: ultimate detector, but not mature enough

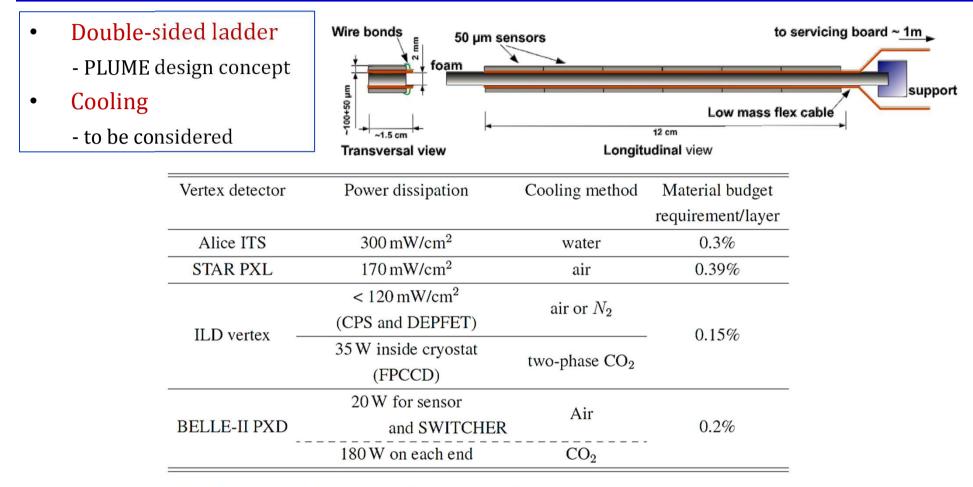

### **Mechanics and Integration**

Table 4.3: Cooling methods for several vertex detector designs. The chip power dissipation, coolant type and corresponding material budget requirement per sensor layer are indicated. The active CO<sub>2</sub> cooling adds additional material in the forward region, outside the sensitive area. For the ILD FPCCD option, this additional material budget is  $0.3\% X_0$  averaged over the end-plate region, while for the BELLE-II PXD, it is  $\sim 0.1 - 0.2\% X_0$  per layer.

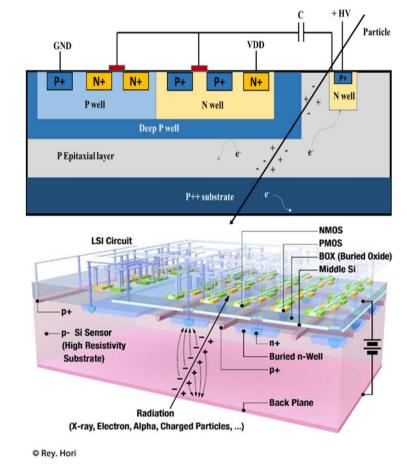

### **R&D** Activities in China

#### Initial sensor R&D targeting on

- Pixel single point resolution <3  $5\mu m$

- Power consumption at the current level <100mW/cm<sup>2</sup>

- Integration time 10-100μs

- Two monolithic pixel technologies

- CMOS pixel sensor (CPS)

- TowerJazz CIS 0.18 µm process

- Quadruple well process

- Thick (~20 μm) epitaxial layer

- with high resistivity ( $\geq 1 \ k\Omega \bullet cm$ )

- SOI pixel sensor

- LAPIS 0.2 µm process

- High resistive substrate ( $\geq 1 \text{ k}\Omega \cdot \text{cm}$ )

- Double SOI layers available

- Thinning and backside process

### CMOS Pixel Sensor – 1<sup>st</sup> Design

- Sensor design & TCAD simulation Y.Zhang, et al, NIMA 831(2016)99-104

- Different sensor diode geometries, epitaxial-layer properties and radiation damage

- JadePix1 submission in Nov. 2015

- Exploratory prototype, analog pixel, rolling shutter readout mode

- Sensor optimization and radiation tolerance study

- sensing node AC-coupled to increase biased voltage

- Sensor characterization

- Noise level

- Charge collection efficiency

- Irradiation with Neutron

- Test beam in Aug. 2018

Y. Zhang, Y.Zhou, et al (IHEP, SDU)

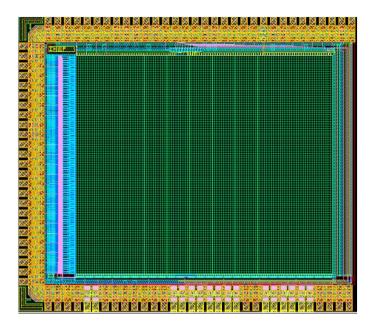

### CMOS Pixel Sensor – 2<sup>nd</sup> Design

Design goal: digital readout pixel sensor with

- Single point resolution better than 5µm

- Power consumption <80  $mW/cm^2$

- Integration time < 100μs</li>

#### **Technology:** *TowerJazz CIS 0.18 µm process*

#### Joint effort of CCNU and IHEP

#### **Design submission** in May 2017

- Tow prototypes with digital pixels (in-pixel discriminator)

- Tow different readout schemes: rolling shutter & asynchronous

#### JadePix2: Y.Zhou (IHEP)

- Pixel size:  $22\mu m \times 22\mu m$

- Two different pixel version with higher biased voltage

- Test in lab ongoing

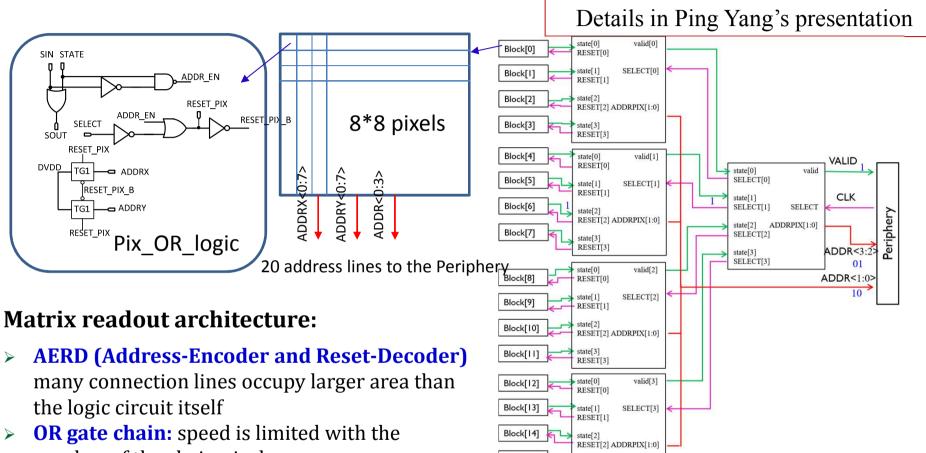

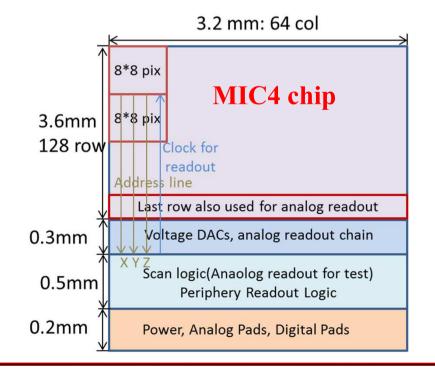

- MIC4: P.Yang(CCNU) Y.Zhou (IHEP)

- Pixel size:  $25\mu m \times 25\mu m$

- Two different pixel front-end with Matrix readout architecture

- Test in lab ongoing

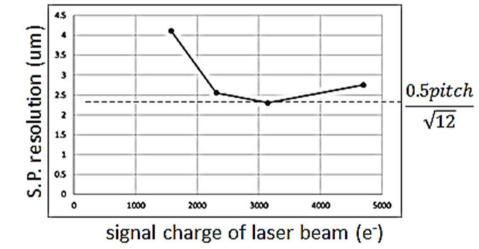

### **R&D** Activities - SOI Pixel Sensor

- First submission (CPV1) in June 2015

- 16\*16 µm with in-pixel-discrimination

- Double-SOI process for shielding and radiation enhancement

- Second submission (CPV2) in June 2016

- In-pixel CDS stage inserted

- To improve RTC and FPN noise

- To replace the charge injection threshold

#### **<u>CPV2 performance</u>**

- Thinned down to 75um thick

- Temporal noise ~6e<sup>-</sup>

- Threshold dispersion (FPN) ~114e<sup>-</sup>

- Single point resolution measurement under infrared laser beam

#### Sept 13-15 , 2018 CEPC physics and detector CDR international review

Y. Lu (IHEP)

Y. Lu, Y.Zhou (IHEP)

### **Future Plan on R&D**

- Further optimization study of vertex system

- Novel readout scheme exploration

- Large area pixel array design

- Radiation hardness and time-stamp sensor design

- Prototype development

- Small ( $16\mu m \times 16\mu m$ ) pixel, targeting on  $3\mu m$  single point resolution

- To explore 3D connection technology by designing the in-pixel digital logic in a separated tier

- Or to look for any new process

#### Summary

- CDR finished with baseline design

- Critical technologies listed

- R&D project started along the baseline design specifications

- in-pixel electronics, small pixel size

- new asynchronous readout architecture

- Collaboration with international teams

- Going to TDR for next step

- Expertise demanding

Many thanks to all members of CEPC Physics and Detector working group who made significant efforts to prepare the CDR !

# Thank you for your attention!

### **CEPC CDR Parameters**

D. Wang

|                                                                      | Higgs           | W             | Z (3T)              | Z (2T)       |  |

|----------------------------------------------------------------------|-----------------|---------------|---------------------|--------------|--|

| Number of IPs                                                        | 2               |               |                     |              |  |

| Beam energy (GeV)                                                    | 120             | 80            | 45                  | 5.5          |  |

| Circumference (km)                                                   |                 | 100           |                     |              |  |

| Synchrotron radiation loss/turn (GeV)                                | 1.73            | 0.34          | 0.036               |              |  |

| Crossing angle at IP (mrad)                                          | 16.5×2          |               |                     |              |  |

| Piwinski angle                                                       | 2.58            | 7.0           | 23.8                |              |  |

| Number of particles/bunch $N_e$ (10 <sup>10</sup> )                  | 15.0            | 12.0          | 8.0                 |              |  |

| Bunch number (bunch spacing)                                         | 242 (0.68µs)    | 1524 (0.21µs) | 12000 (25ns+10%gap) |              |  |

| Beam current (mA)                                                    | 17.4            | 87.9          | 461.0               |              |  |

| Synchrotron radiation power /beam (MW)                               | 30              | 30            | 16.5                |              |  |

| Bending radius (km)                                                  |                 | 10.7          |                     |              |  |

| Momentum compact (10-5)                                              |                 | 1.11          |                     |              |  |

| $\beta$ function at IP $\beta_{y}^{*} / \beta_{y}^{*}$ (m)           | 0.36/0.0015     | 0.36/0.0015   | 0.2/0.0015          | 0.2/0.001    |  |

| Emittance $\varepsilon_{\nu}/\varepsilon_{\nu}$ (nm)                 | 1.21/0.0031     | 0.54/0.0016   | 0.18/0.004          | 0.18/0.0016  |  |

| Beam size at IP $\sigma_{\rm y}/\sigma_{\rm y}$ (µm)                 | 20.9/0.068      | 13.9/0.049    | 6.0/0.078           | 6.0/0.04     |  |

| Beam-beam parameters $\xi_n/\xi_n$                                   | 0.031/0.109     | 0.013/0.106   | 0.0041/0.056        | 0.0041/0.072 |  |

| RF voltage $V_{RF}$ (GV)                                             | 2.17            | 0.47          | 0.10                |              |  |

| RF frequency $f_{RF}$ (MHz) (harmonic)                               |                 | 650 (2168)    | 16)                 |              |  |

| Natural bunch length $\sigma_{z}$ (mm)                               | 2.72            | 2.98          | 2.42                |              |  |

| Bunch length $\sigma_z$ (mm)                                         | 3.26            | 5.9           | 8.5                 |              |  |

| Betatron tune $v_x/v_y$                                              | 363.10 / 365.22 |               |                     |              |  |

| Synchrotron tune $v_c$                                               | 0.065           | 0.0395        | 0.028               |              |  |

| HOM power/cavity (2 cell) (kw)                                       | 0.54            | 0.75          | 1.94                |              |  |

| Natural energy spread (%)                                            | 0.1             | 0.066         | 0.038               |              |  |

| Energy acceptance requirement (%)                                    | 1.35            | 0.4           | 0.23                |              |  |

| Energy acceptance by RF (%)                                          | 2.06            | 1.47          | 1.7                 |              |  |

| Photon number due to beamstrahlung                                   | 0.29            | 0.35          | 0.55                |              |  |

| Lifetime _simulation (min)                                           | 100             |               |                     |              |  |

| Lifetime (hour)                                                      | 0.67            | 1.4           | 4.0                 | 2.1          |  |

| F (hour glass)                                                       | 0.89            | 0.94          | 0.99                |              |  |

| Luminosity/IP L (10 <sup>34</sup> cm <sup>-2</sup> s <sup>-1</sup> ) | 2.93            | 10.1          | 16.6                | 32.1         |  |

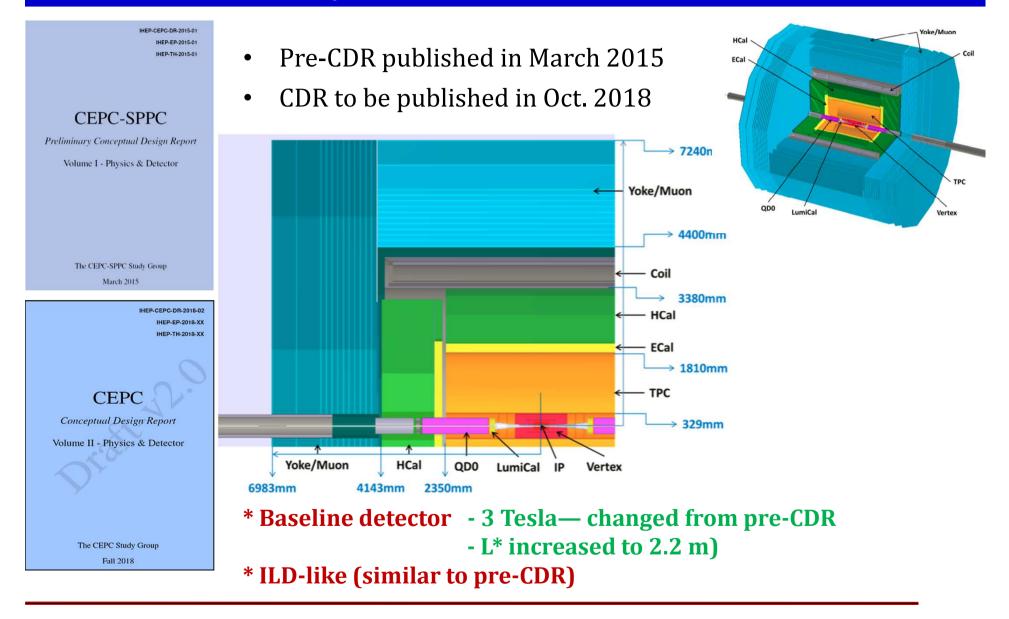

#### **Physics & Detector CDR**

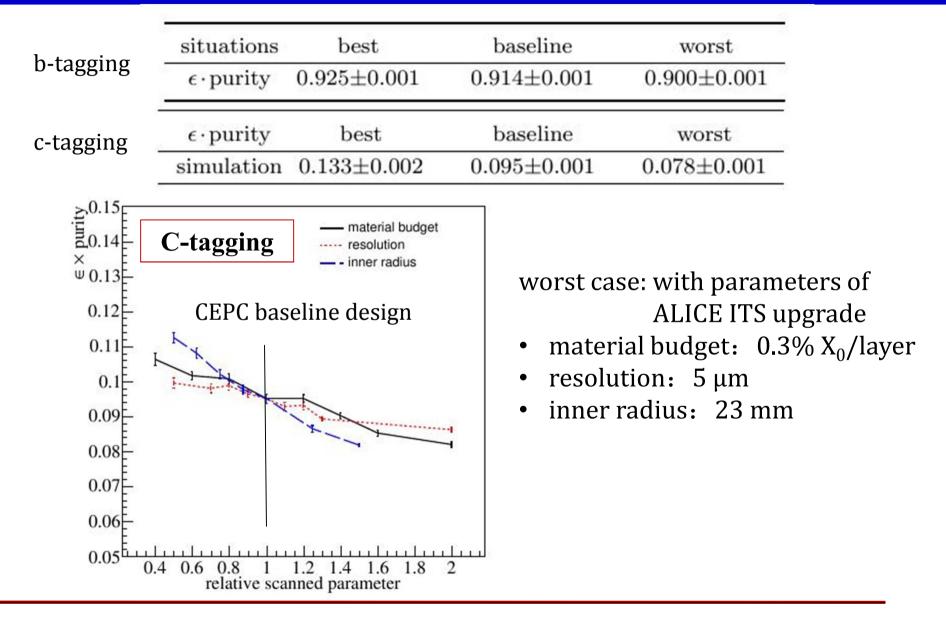

#### **Performance Studies – Flavour Tagging**

### **Performance Studies – IP Resolution**

Sept 13-15, 2018 CEPC physics and detector CDR international review

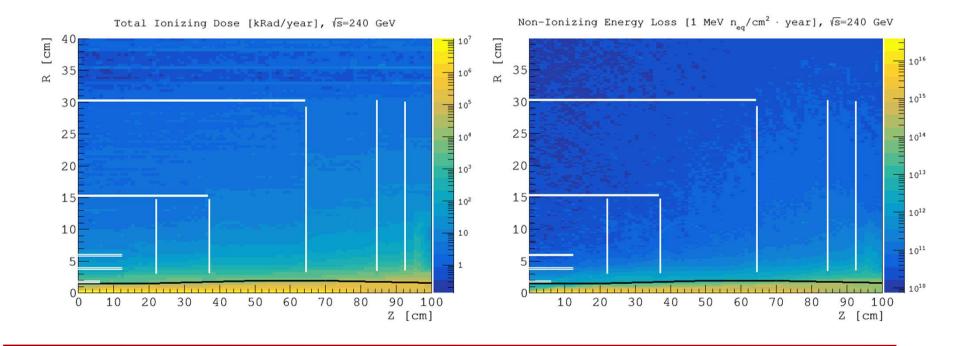

### **Radiation Background Levels**

H. Zhu, CEPC Workshop Rome May 24-26 2018

- Using hit density, total ionizing dose (TID) and non-ionizing energy loss (NIEL) to quantify the radiation background levels

- Adopted the calculation method used for the ATLAS background estimation (ATL-GEN-2005-001), safety factor of ×10 applied

Sept 13-15, 2018

CEPC physics and detector CDR international review

### JadePix2: Rolling - shutter Mode

#### Two different pixel versions:

- Pixel size:  $22\mu m \times 22\mu m$

- Same amount of transistors;

- Offset cancellation technique;

- Version 2 has higher signal gain, but suffers "more" from "Latch" input voltage distortion.

Details in Yang Zhou's presentation

#### **Chip features:**

- $3 \times 3.3 \text{ mm}^2$

- 96 $\times$ 112 pixels with 8 sub-matrix

- Processing speed: 11.2µs/frame with 100 ns/row

- Output data speed: 160 MHz

- Power: 3.7μA/pixel (14.4 mW/cm<sup>2</sup> @pixel matrix)

### **MIC4 Design: Asynchronous Mode**

Block[15]

state[3] RESET[3]

number of the chain pixels

Combine these two solutions: 64 pixels as a group using OR gate chain, groups using AERD structure to readout

front-end I: ALPIDE structure P. Yang (CCNU) front-end II: CSA based front-end circuit Y. Zhang (IHEP)

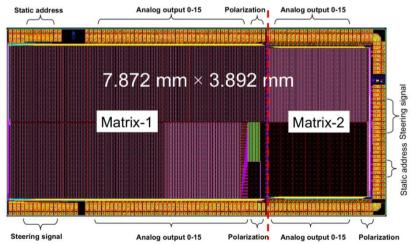

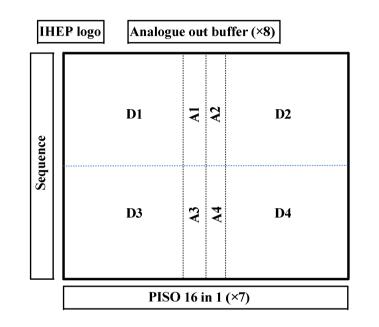

### **MIC4 Submission: Asynchronous Mode**

#### Y. Zhang (IHEP) & P.Yang (CCNU)

#### front-end I: Same structure as ALPIDE chip

- ENC: 8 e<sup>-</sup>

- Power cons.: 61 nA/pixel

- Threshold: 140 e<sup>-</sup>

- Peaking time < 1 us

- Pulse duration < 3  $\mu$ s

#### front-end II: CSA based front-end circuit

- Pixel size:  $25\!\times\!25\,\mu m^2$

- ENC: 24 e<sup>-</sup>

- Power cons.: 50 nW/pixel (8 mW/cm<sup>2</sup> @pixel matrix)

- Threshold: 170 e<sup>-</sup>

- Peaking time < 500 ns @ Qin < 1.5 ke<sup>-</sup>

- Pulse duration < 9.4  $\mu$ s @ Qin < 1.5 ke<sup>-</sup>

- > 3.2  $\times$  3.7 mm<sup>2</sup>

- $\succ$  128  $\times$  64 pixels

- Integration time: < 5 μs/10 μs</p>

- Power consumption: < 80 mW/cm<sup>2</sup>

- Chip periphery

- Band gap

- Voltage DAC

- Current DAC

- Matrix configuration

- LVDS

- Custom designed PADs