中國科學院為能物況加完所 Institute of High Energy Physics Chinese Academy of Sciences

# **Analog front-end design**

Ying ZHANG

2018-9-10

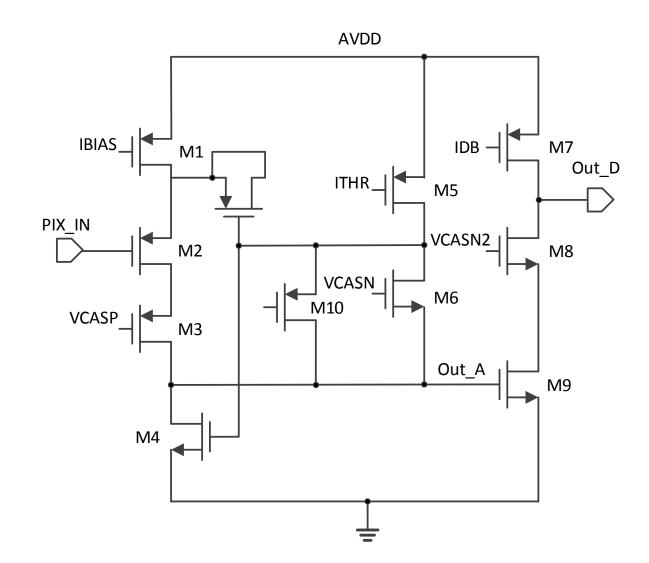

## **Front-end design**

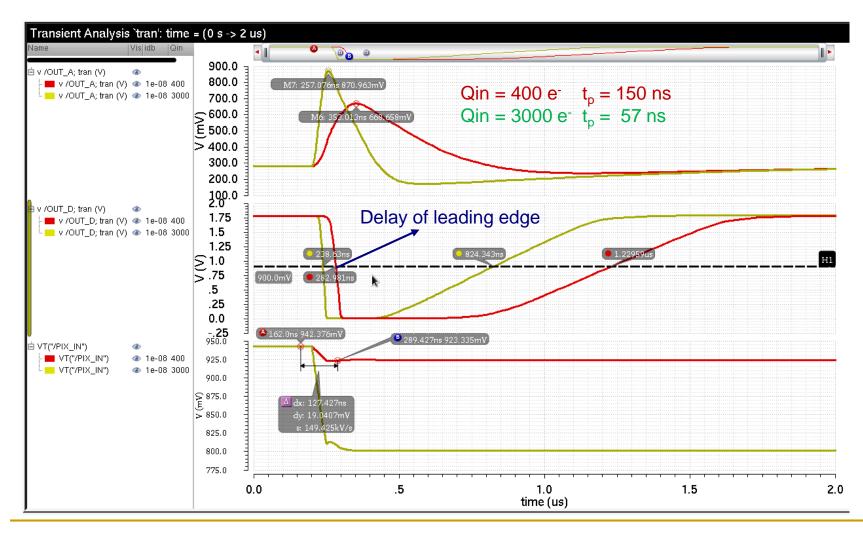

## **Front-end simulation**

#### Simulation condition: Cd = 2.5 fF, IBIAS = 440 nA

## **Front-end simulation**

Simulation condition: Cd = 2.5 fF, IBIAS = 440 nA

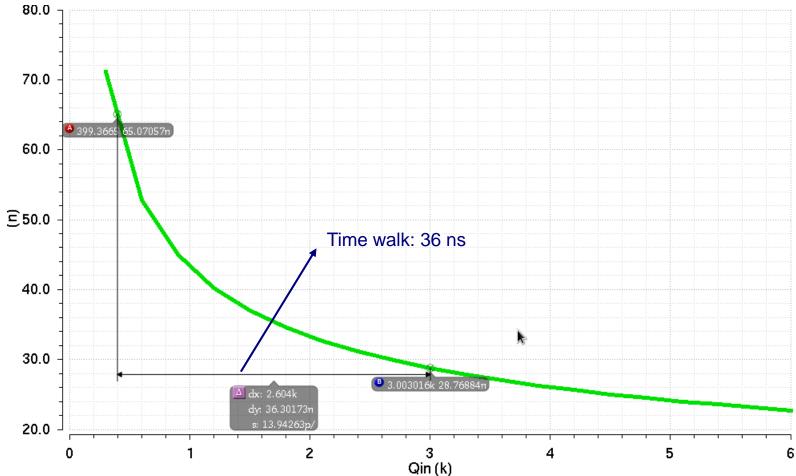

#### Delay of leading edge vs. input charge

MOST2 CEPC-VTX Chip Design, Ying ZHANG

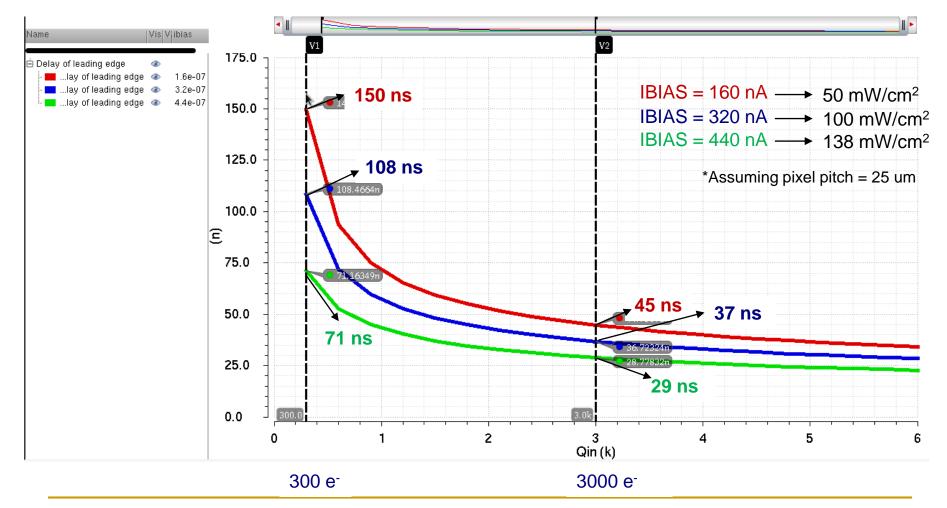

## **Front-end simulation**

Simulation condition: Cd = 2.5 fF,  $Qin = 50 \text{ e}^2 - 6k \text{ e}^2$ , 3 different IBIAS

#### Delay of leading edge vs. input charge

MOST2 CEPC-VTX Chip Design, Ying ZHANG

## **Discussion and next step**

#### How fast do we need?

- Peaking time? Time walk?

- > Compromise between time performance and power consumption

#### Next step: noise and mismatch need to be verified and optimisation

## Backup

# **MALTA chip for ATLAS**

## **Analog Performance**

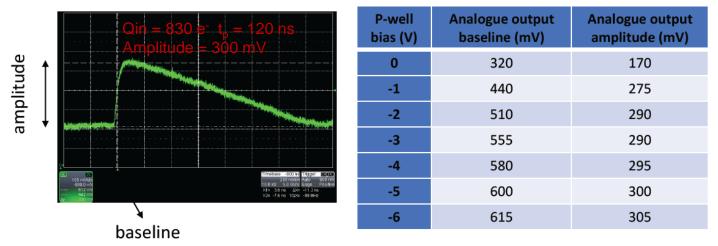

- Measured analog output signal (OUT\_A) of the front-end on monitoring pixels in sector 0 (diode reset) after test pulse injection

- $V_{SUB}$  = 6 V, pulsing with  $V_{HIGH}$  = 1.78 V and  $V_{LOW}$  = 1.2 V ( $\approx$  830 e-equiv ½ MIP)) W4R7

• + 10% increase in signal when going in  $V_{SUB}$  from -6 to -20 V

| 17/04/18 Abhishek Sharma 8 |          | A. Sharma, 17 <sup>th</sup> April 2018, A | TLAS Upgrade Week |

|----------------------------|----------|-------------------------------------------|-------------------|

|                            | 17/04/18 | Abhishek Sharma                           | 8                 |

# **MALTA chip for ATLAS**

# **Analog Performance**

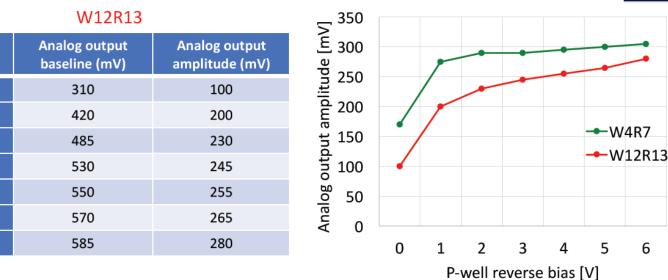

- Chip from wafer 4 has slightly higher gain than wafer 12 (consistent with previous measurements on the TJ Investigator chip)

- All subsequent tests performed at  $V_{SUB}$ = -6 V and  $V_{PWELL}$ = -6 V

P-well

bias (V)

0

-1

-2

-3

-4 -5

-6

Abhishek Sharma

9