# Status of Digital Pixel

Tianya Wu CEPC MOST2 Chips Meeting

twu@ifae.es

19-11-2018

d'Altes Energies

Barcelona Institute of Science and Technology

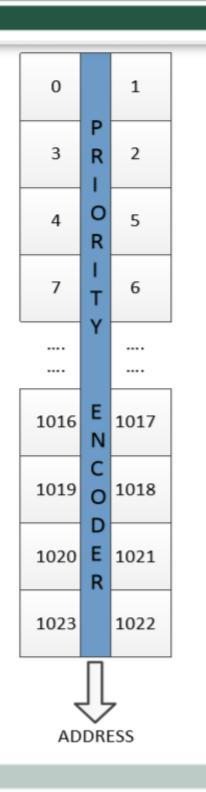

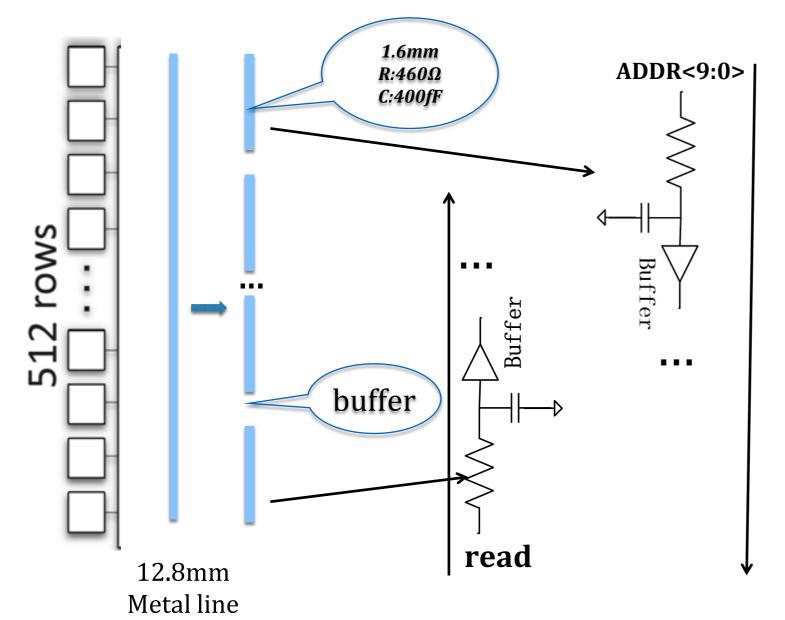

#### Double column structure

- The matrix of pixels is read out by an array of 1024

Priority Encoder blocks.

- The pixels are arranged in double columns and the regions at the middle of each double column are occupied by the Priority Encoders.

- The indexing of the pixels in the readout data words is defined by the Priority Encoders.

- Top pixels have highest priority.

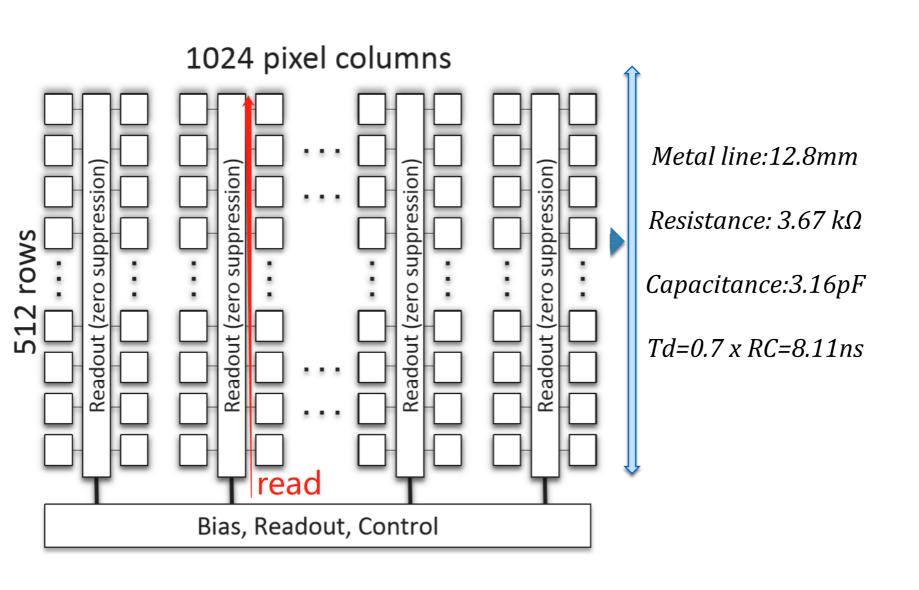

## Parasitic resistor and capacitor simulation

- The read signal start from end of column, the worst case delay of the read out occurs when the first row of pixels is hit.

- The schematic can't work with such a big load.

## Optimize the delay with buffers

- Divide into 8 segments

- > Insert 8 buffers

- The delay of each segment is: td\_seg=0.13ns

- The delay of buffer: td\_buf=0.11ns

- Total delay:

td\_total=1.92ns <Td(8.11ns)</p>

to drive the long

metal line. There

exists an obvious

distortion.

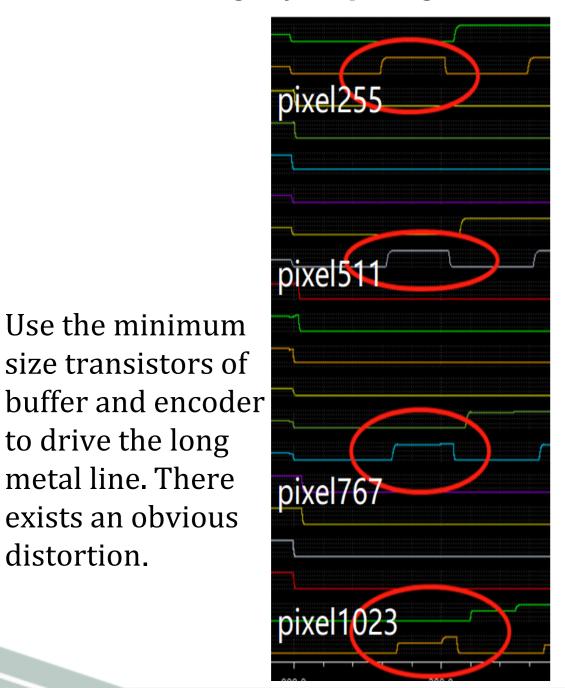

#### Parasitic simulation

The change of output signal ADDR<0> pass from pixel\_0 to pixel\_1023

pixel255 pixel511 pixel767 pixel1023

Enhance the driving strength of the output stage(Buffers and encoders). All pmos dimension is 3 times lager than the nmos at output stage.

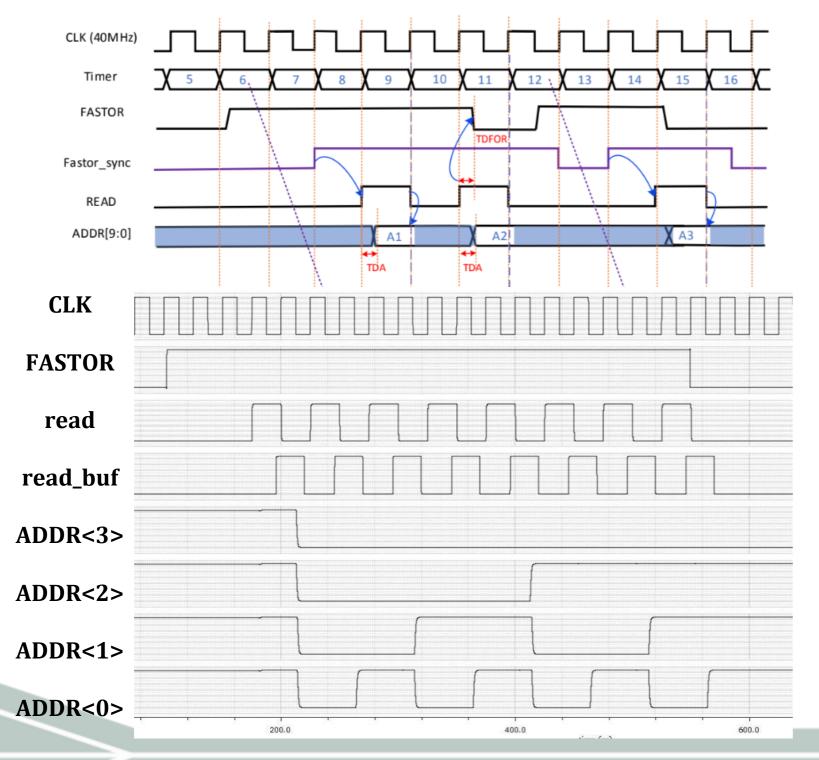

## The evaluation of total delay

| TT; 1.8V; 27°C |         |

|----------------|---------|

| Signal         | Delay   |

| FASTOR         | 1.7ns   |

| read           | 14.35ns |

| TDA            | 26.75ns |

| TDFOR          | 16.36ns |

| SS; 1.6V; 50°C |          |

|----------------|----------|

| Signal         | Delay    |

| FASTOR         | 2. 527ns |

| read           | 20. 67ns |

| TDA            | 39. 33ns |

| TDFOR          | 24.11ns  |

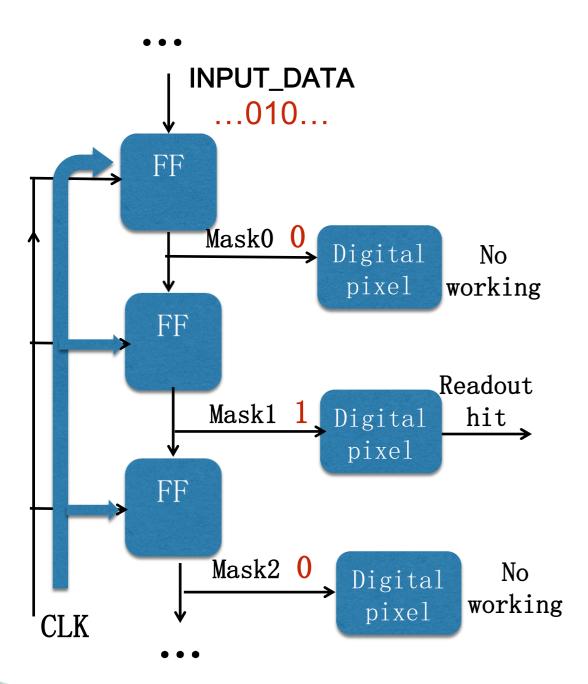

### The evaluation of masking circuits

- CLK of 1bit shifting register works from bottom to top.

- Masking data start from top.

- Total CLK delay of masking circuits is around 12.5ns.

Column with 1024 pixels

#### **OUTLOOK**

- I simulated the parasitic r&c with the estimated value, the layout should be done to ensure the circuits performance.

- I need determine the area of digital pixels.

- The layout of priority encoder is challenging, I need some expert help on the digital layout.

# Thanks for your attention.