## Hardware development for TDAQ based on xTCA

Jingzhou ZHAO<sup>1</sup>, Zhen-An LIU<sup>1</sup>, Wenxuan GONG<sup>1</sup>, Pengcheng CAO<sup>1</sup>, Wolfgang Kuehn<sup>2</sup>

- 1. Trigger Lab, Institute of High Energy Physics, Chinese Academy of Sciences

- 2. II. Physikalisches Institut, Justus-Liebig-Universität Gießen

MTCA/ATCA workshop 2019, IHEP,Beijing

### Outline

- **#** Requirements to TDAQ system

- **¤** xTCA for Physics

- CN\_V3 for Belle II PXD DAQ

- **#** CN\_V4 for PANDA DAQ

- **CPPF** for CMS trigger system

**#** summary

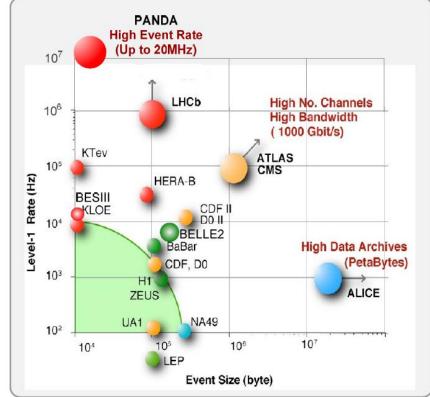

# Requirements to TDAQ system

- Future Physical experiment accelerator and Spectrometer

- > High luminosity

- ➤ CEPC(90-350GeV,

- > CEPC( $10^{34}$ cm<sup>-2</sup>s<sup>-1</sup>~ $10^{35}$ cm<sup>-2</sup>s<sup>-1</sup>)

- High data event rate

- > PANDA (20MHz)

- > CEPC(40MHz)

#### **#** Requirements to TDAQ system

- High speed data transmission;

- High performance data processing;

- Mass data buffering

#### Standards for Nuclear Instrumentation

Beijing

- **#** 1960's

- NIM: American Standard Beurea and NIM Module Committee

- 70-80's CAMAC, FASTBUS, widely used

Nuclear Spectrum Measurement,

Particle Physics, Medical Physics,

Accelerator Instrument, Accelerator

Control, Aerospace, Industrial control.

- **•** 90's VME from Industry

- **♯** 2000 CPCI

- **•** Still in use, BUT limited by bandwith.

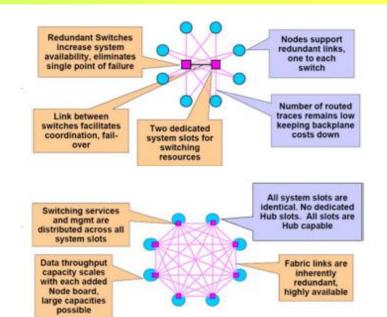

# xTCA for Physics

#### ATCA ->PIGMG3.8

- Advantages

- High speed IO and 10Gbps-25Gbps interconnections

- HA ~99.999%

- IP management

- Add control signal

- •MicroTCA (MTCA) ->MTCA 4.0

- Advantages of ATCA

- Half height, compact system

- add rear transition board and control

- AdvancedMC (AMC)

- Modular design

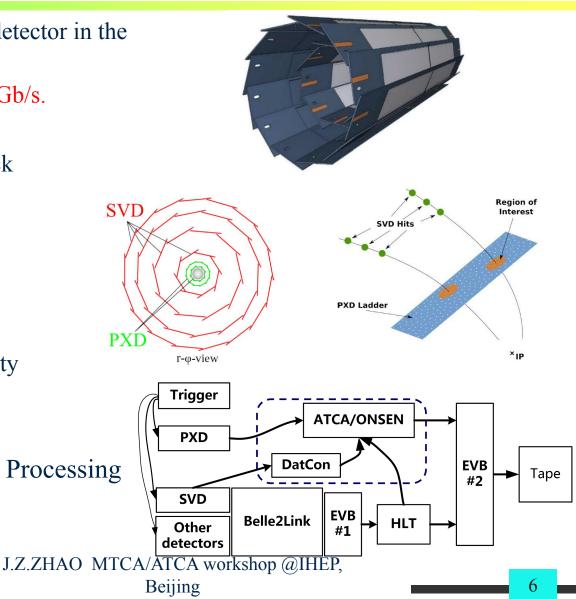

### Compute Node for Belle II PXD DAQ

- PXD detector is a new detector in the upgrade of Belle II.

- **\ddagger** Huge data output:  $\sim 200$ Gb/s.

- **# PXD** reduction

- Help with SVD track

- **1/10**

- Tracking back

- ROI searching

- Data extraction

- **#** Difficulties

- Computing capability

- Algorithms

- 5s data buffer

- Data sharing between Processing node

#### Compute Node for Belle II PXD DAQ

- **#** High Performance FPGA is used for data processing,

- RocketIOs are used for high speed data transmission between data processing node,

- **#** DDR is used for mass data buffering,

- **#** ATCA/xTCA architecture is used for PXD DAQ,

- Intelligent platform management control system is used for system stable.

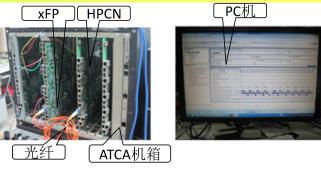

# Key parts of PXD-DAQ

ONSEN/PXD-DAQ

- Firmware( Giessen Uni)

- Hardware(IHEP Beijing)

- 1 ATCA Shelf

- 2 shelf managers

- 1 Power Supply

- 9 Compute Node(CN)

- 1 ATCA Carrier(PICMG3.8)

- 1 RTM

- 1 Power Board

- 4 xFP/AMC cards

- 1 IPMC+ 4 MMCs J.Z.ZHAO MTCA/ATCA workshop @IHEP,

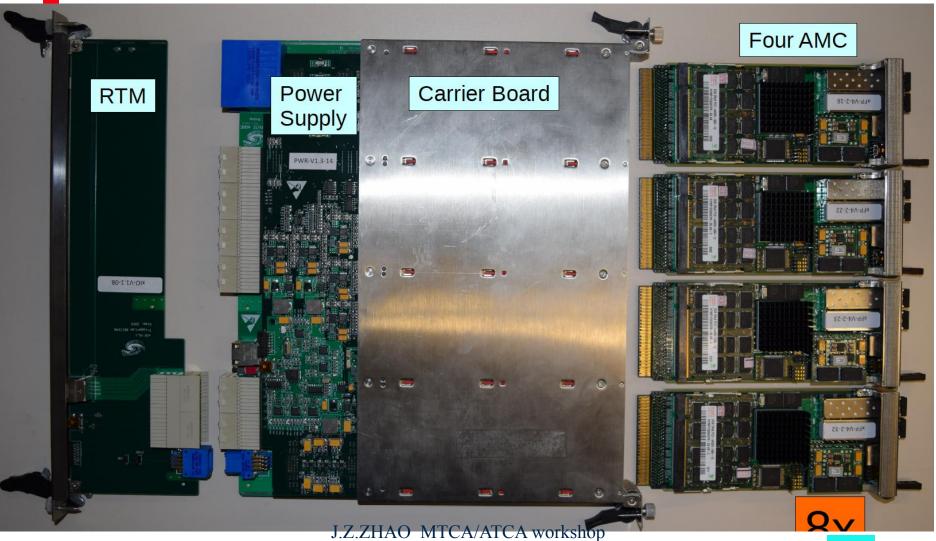

### Full Compute Node for PXD DAQ

@IHEP, Beijing

9

2019/06/23

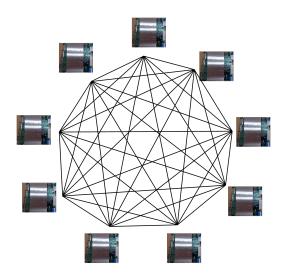

### Full Mesh for PXD DAQ

- Full mesh backplane for CN data sharing with each node.

- Full mesh on board connection for AMC cards.

- **#** Point to Point via one MGT channel,

- Line rate up to 3.125Gbps.

Full mesh backplane connection

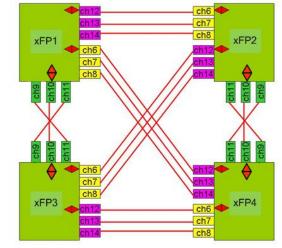

Ch6-12, pin definition of AMC connector

Connectivity on carrier board, each channel has one input differential pair and one output differential pair

Full mesh on board connection for AMC

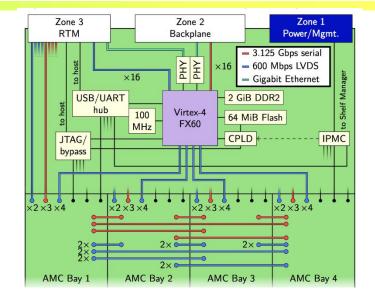

### CNCB(CN Carrier Board)

- **#** Function of CN Carrier Board V3.3

- > Virtex-4 FX60 with PowerPC405,

- > Embeded linux system for slow control,

- > 16 RocketIO channel connect to backplane,

- > 2GB DDR2,

- > 2 Ethernet ports,

- > IPMC

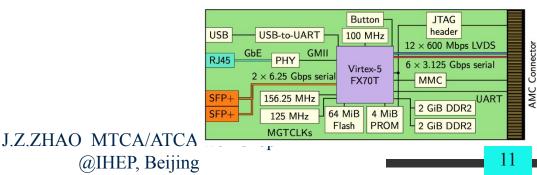

- **#** Function of AMC

- > Virtex-5 FX70T with PowerPC440,

- > Embeded linux system for data management,

- > 2 SFP+ port, 6.25Gbps/ch

- > 4GB DDR2,

- > 1 Ethernet ports,

- > UART port,

- > MMC

### Status of Belle II xTCA PXD-DAQ

12

- **F**rist Beam test in DESY in 2014

- **#** Second BT in 2016

- The whole DAQ chain was tested with up to 2kHz, Long time stability tested for 8h.

- Everything stably watched by run and slow control

- **#** Complished in 2016

- Mass Production 2015

- System integration Nov.2016

- Now whole system is being integrated with detector in KEK for data taking.

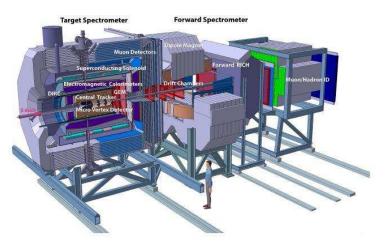

# PANDA DAQ system

- PANDA is a next generation hadron physics detector planned to be operated at the future Facility for Antiproton and Ion Research(FAIR) at Darmstadt, Germany.

- High event Rate: up to 20MHz,

- Each event: 1.5Kbyte-4.5Kbyte,

- Considering electronic noise, background and signal accumulation, DAQ should has ability of data processing about 200GBps.

How to deal with such big data with NO Dead Time is a great challenge to DAQ system.

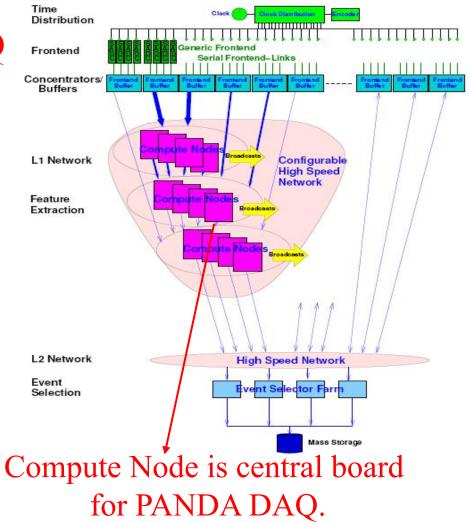

# PANDA DAQ

# Trigger-less streaming DAQ with event filtering

- Global time distribution for time stamping,

- L1 Network,

- Extract particle information like energy, position, momentum and so on;

- - Make a preliminary reconstruction for physics events;

- Event selection will be done based on the research topics of PANDA experiment.

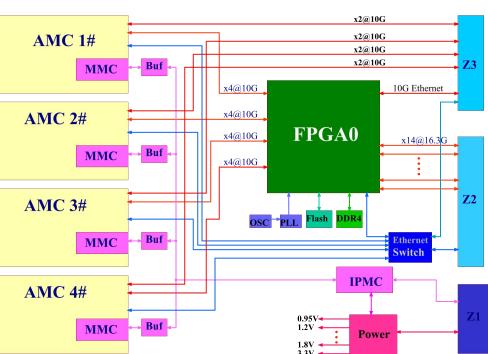

### Compute Node for PANDA

- **FPGA:** Ultrascale Kintex xcku060

- **RAM:** 16 GB DDR4 (8 chips)

- **# MGTs:** 16.3 Gbps

- 4 links to each AMC card;

- 12 links to ATCA backplane;

- 1 link to RTM (10G Ethernet);

- **GbE** switch:

- 4 AMCs,

- 1 switch FPGA,

- 1 uplink to ATCA Base Interface

- 1 RTM RJ45

- 10 Gigabit Ethernet to RTM(SPF+)

- **Configuration:** automatic from NOR Flash (master BPI)

- **#** Programmable MGT clock

- **#** CPLD as **JTAG hub**

- **♯** IPMC/MMC

#### 2019/06/23

### First Version of CNV4.0

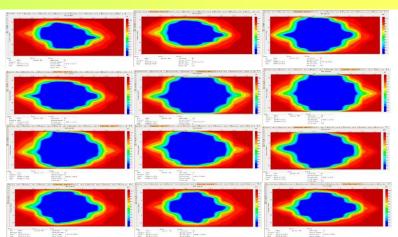

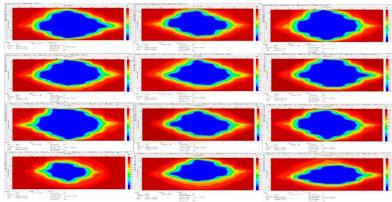

### CN Backplane MGT channel test

#### Crate:

- Two ATCA Slots,

- 12 Backplane channel point-to-point, connection between two slots,

- 25Gbps/ch for Backplane connector.

- ◆ 24 hours, No error on 12.5Gbps.

- Error rate <1E-15.

#### Backplane MGT 10G 12channel

#### Backplane MGT 12.5G 12channel

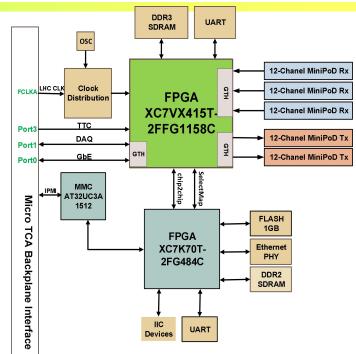

# CPPF for CMS trigger system

- Based on MicroTCA protocol

- Two Xilinx FPGA chips for board controlling and functionalities implement

- ☎ 36 optical links input,

- 24 optical links output,

- **♯** Support 10Gbps/ch

- ➡ CPPF system was successfully integrated in CMS trigger system in May of 2017.

- **x**TCA is the Next Trigger/DAQ standard for physical experiment.

- **#** CN V3 is designed and successful used for Belle II PXD DAQ.

- **#** CN V4 is designed successfully for PANDA DAQ.

- CPPF has been desinged and used on CMS Phase-I upgrade successfully.

- New Compute Node is being developed for CMS PhaseII upgrade according to the requirement.

# Thanks for your attention and comments.