# Status of Digital Pixel

Tianya Wu CEPC MOST2 Chips Meeting

twu@ifae.es

04-03-2019

Barcelona Institute of Science and Technology

#### **OUTLINE**

- ALPIDE logic block

- FE\_I3 logic block

- Outlook

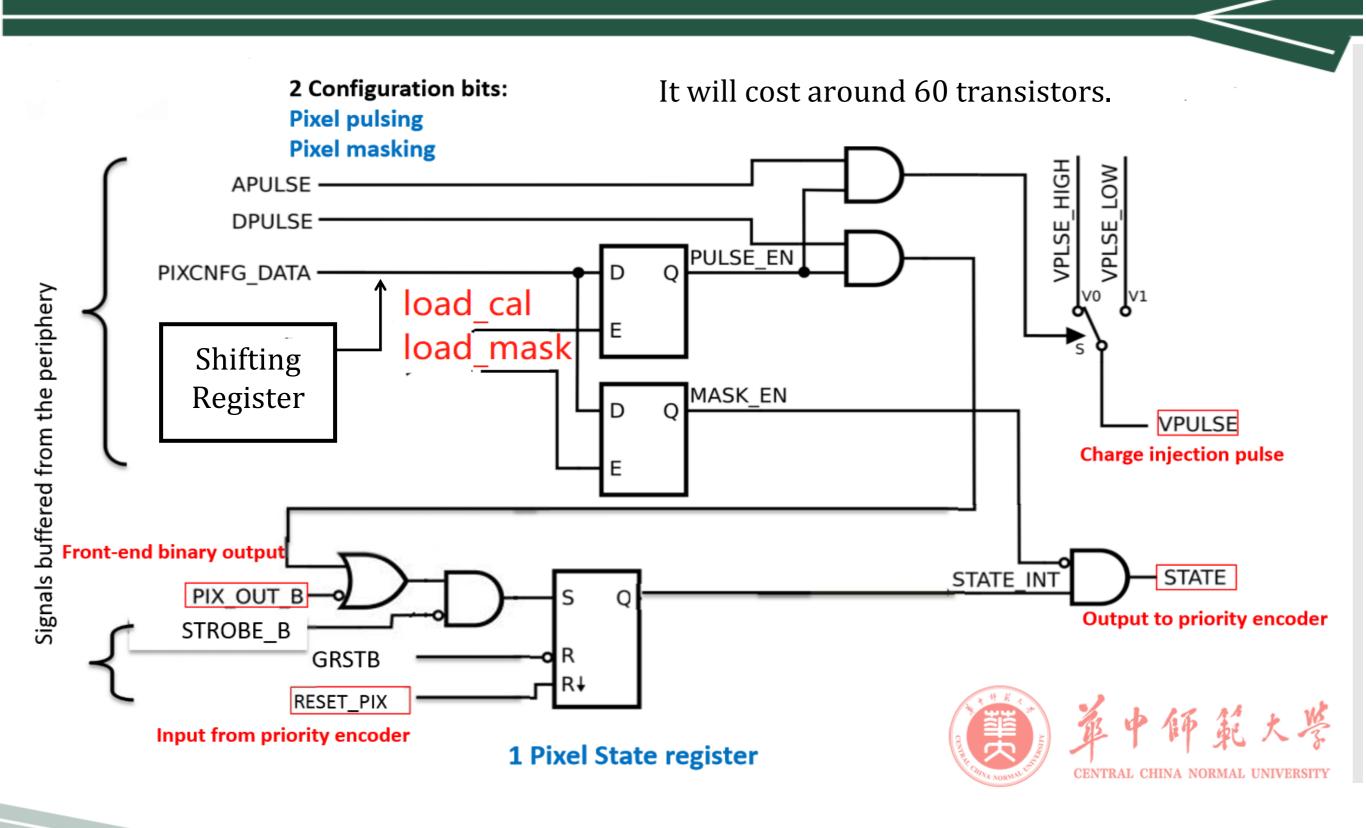

## **ALPIDE Digital Cell**

## **Optional Digital Cell**

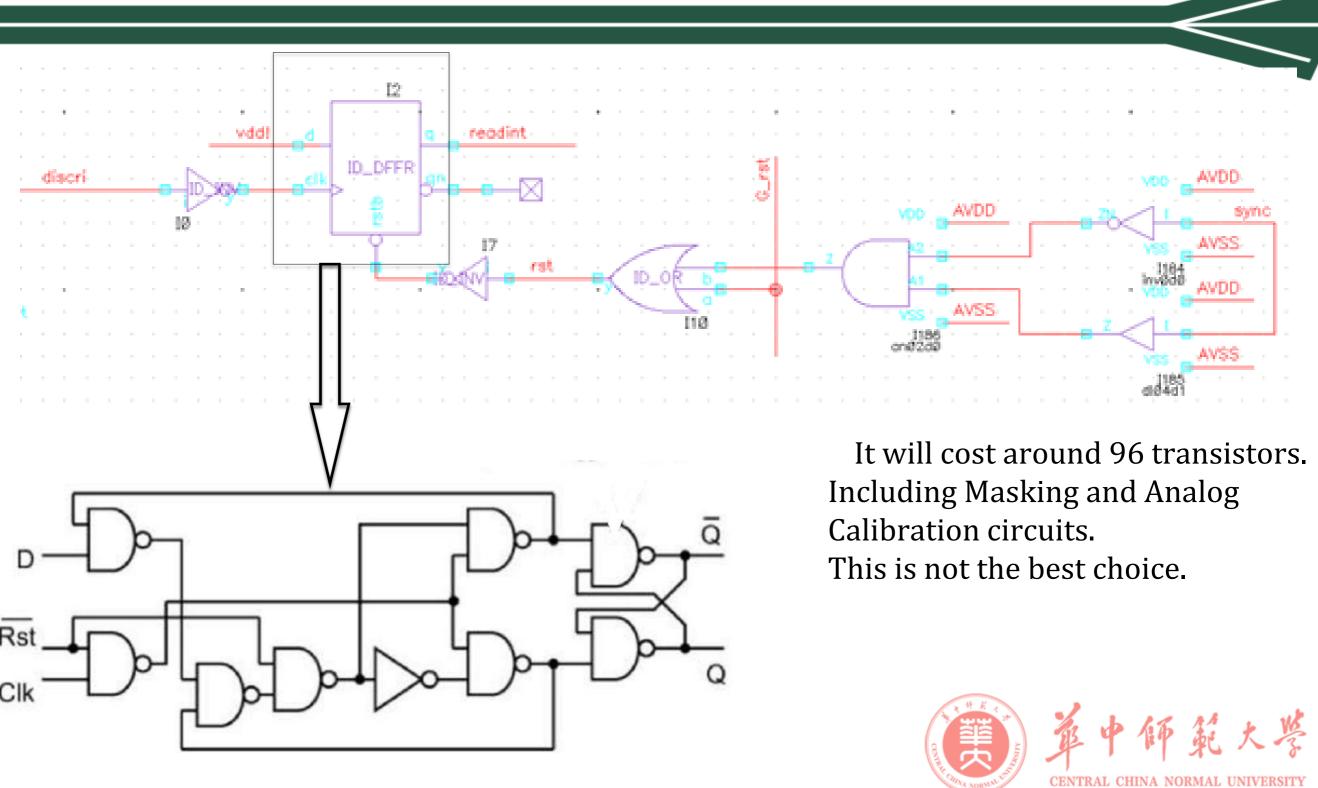

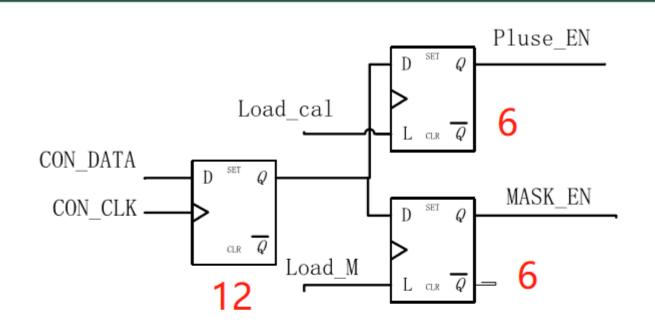

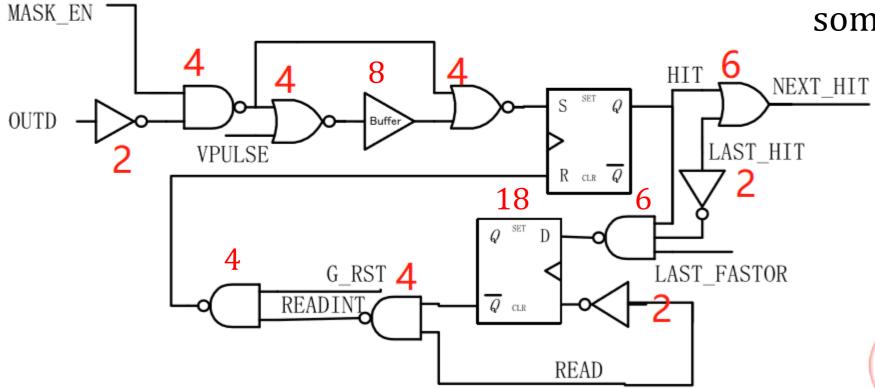

### FE-I3 Digital Cell

It will cost around 104 transistors, including the Analog calibration block.

But the address encoder part will save some area than ALPIDE

#### Conclusion and OUTLOOK

#### Conclusion:

- From my simulation result, the ALPIDE structure will need a trigger latency signal (Strobe) more to reduce the effect of analogue pulse duration.

- Both of them are working fine with the external configuration bits.

#### *Next tasks to do:*

- Do the standard cell layout.

- Simulate the full column and submit it.

# Thanks for your attention.