UNIVERSITÄT HEIDELBERG

Ming Zeng<sup>1</sup>, Guanghua Gong<sup>1</sup>, Zhenwei Yang<sup>1</sup>, Li Xu<sup>1</sup>, Yuyue Gan<sup>1</sup>,

Albert Comerma<sup>2</sup>, Xiaoxue Han<sup>2</sup>

<sup>1</sup>Department of Engineering Physics, Tsinghua University

<sup>2</sup>Physikalisches Institut, Universität Heidelberg

CLHCP 2019

大连 2019.10.26

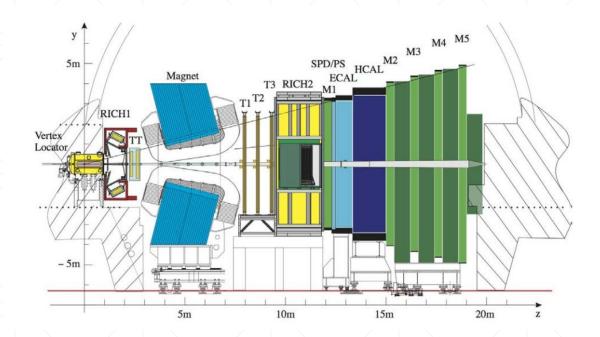

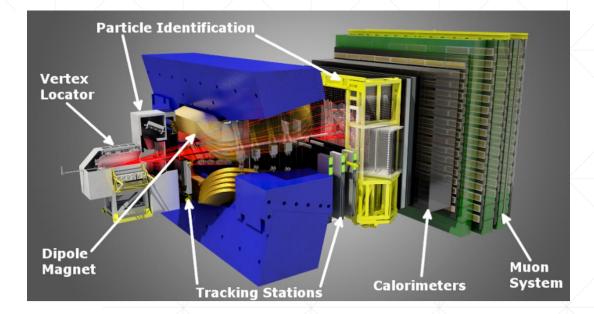

### LHCb 主要科学目标与探测器

- 理解正反物质不对称: CP破坏

- ・ 间接发现新物理:稀有衰变

- 理解强相互作用机制:强子性质,新强子态

- 其它: 电弱物理, 重离子物理, ...

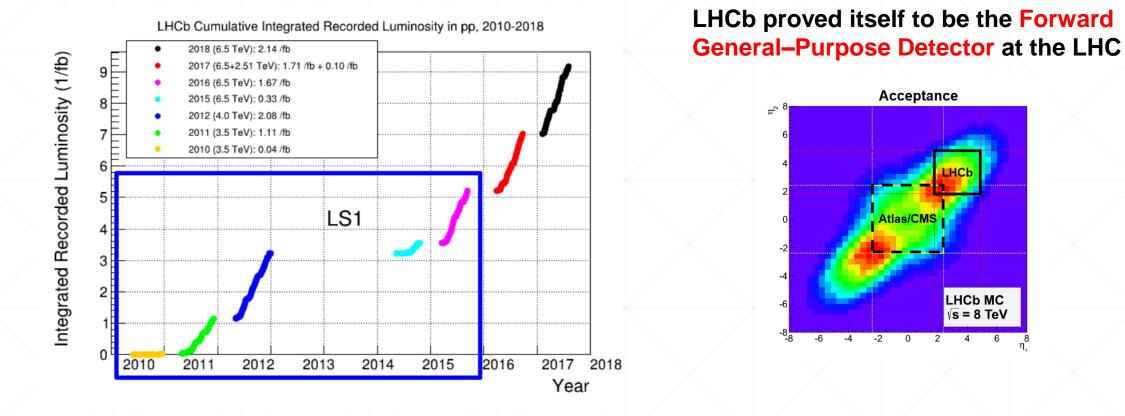

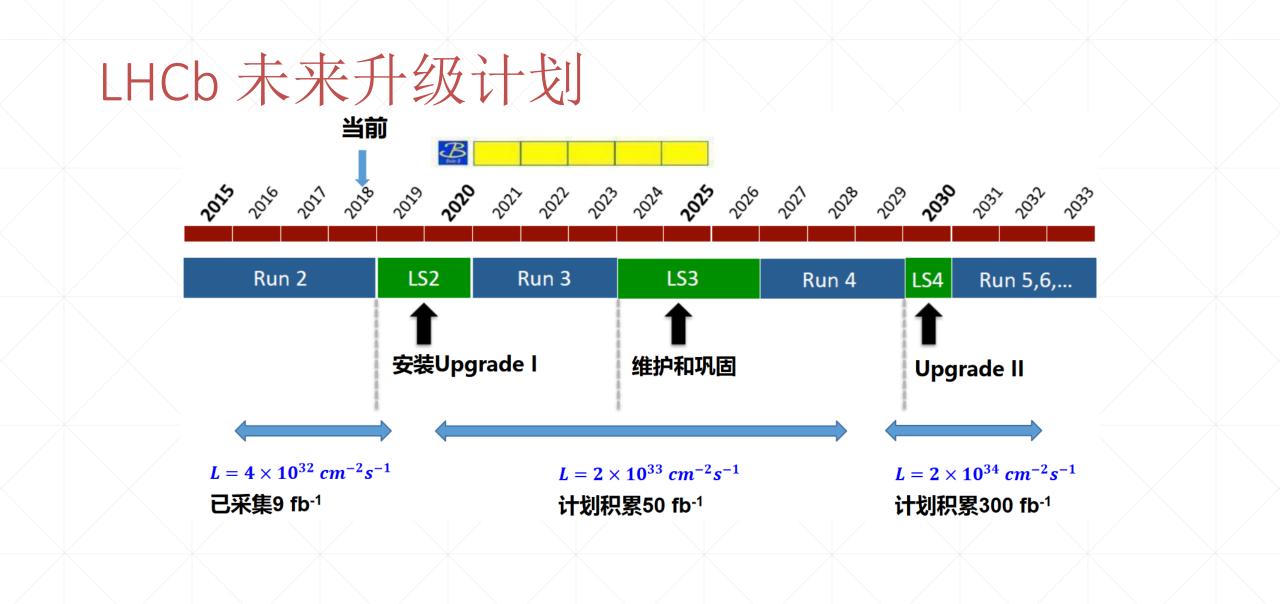

# LHCb Run 2

- > 运行亮度达到 $4 \times 10^{32} cm^{-2} s^{-1}$ ,两倍于设计指标

- ▶ 积分亮度超过9fb<sup>-1</sup>

### LHCb Upgrade Motivation

LHCb Upgrade I, with installing in 2019-2020 (LHC LS2) and first

data-taking in Run 3 (2021-2023).

- **\clubsuit** Goal: increase statistics by more than imes10

- \* Raise operational luminosity by factor of five to  $2 \times 10^{33}$  cm<sup>-2</sup>s<sup>-1</sup>

- Triggerless 40MHz readout (Full software trigger)

- Necessitates redesign of several sub-detectors and overhaul of readout (40MHz readout rate)

- Replace tracking detectors (finer granularity to cope with

higher particle density)

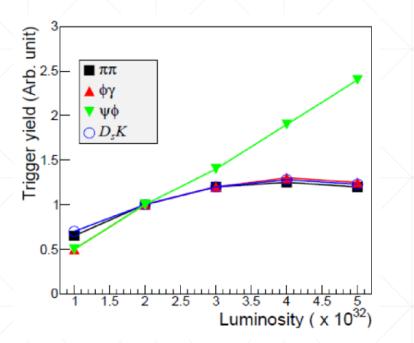

Present L0 hardware trigger (max rate 1 MHz) saturates at high luminosity for hadronic final state modes

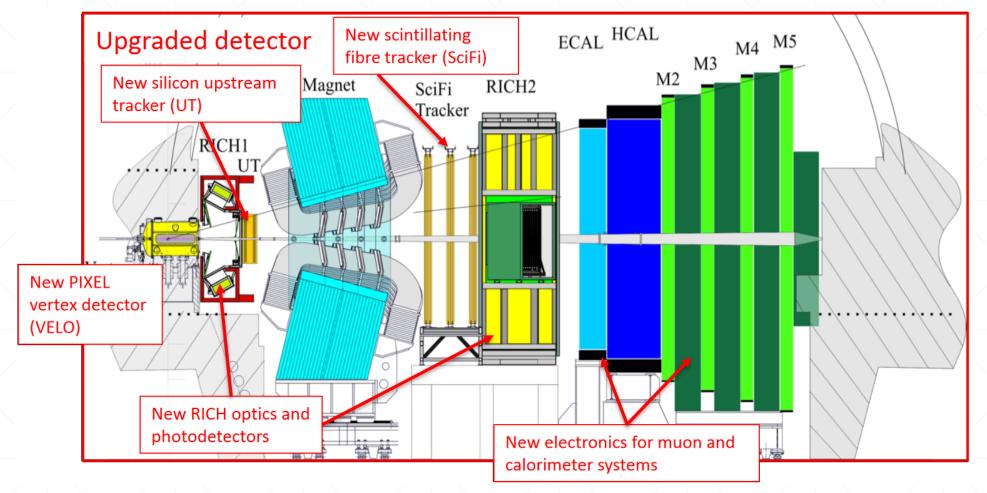

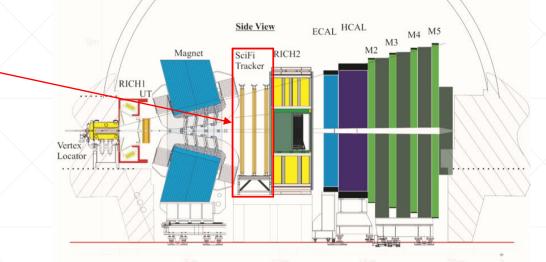

### LHCb Upgrade I

All sub-detectors read out at 40 MHz for a fully software trigger.

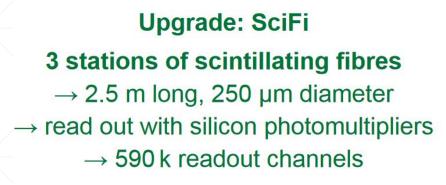

### LHCb Upgrade I: Tracking - SciFi

Current: IT & OT 3 stations with 4 layers each  $\rightarrow$  silicon micro-strips in innermost region  $\rightarrow$  straw drift tubes in outer region  $\rightarrow$  130 k + 54 k readout channels

### LHCb Upgrade I: Tracking - SciFi

Current: IT & OT3 stations with 4 layers each $\rightarrow$  silicon micro-strips in innermost region $\rightarrow$  straw drift tubes in outer region $\rightarrow$  130 k + 54 k readout channels

#### Upgrade: SciFi 3 stations of scintillating fibres $\rightarrow$ 2.5 m long, 250 µm diameter $\rightarrow$ read out with silicon photomultipliers $\rightarrow$ 590 k readout channels

# LHCb Upgrade I: SciFi

### LHCb Upgrade I: SciFi

Goal: increase statistics by more than ×10

✓ Operate at 2×10<sup>33</sup>cm<sup>-2</sup>s<sup>-1</sup> → 50 fb<sup>-1</sup>

✓ Triggerless 40MHz readout

Scintillating Fibre (Sci-Fi) Tracker

✓ Fast, high efficiency (~99%)

✓ High granularity (250µm)

✓ High resolution (<100µm)</li>

✓ Low mass (<1% X<sub>0</sub>/layer)

✓ Radiation hardness (up to 35kGy)

Schematic view of the current LHCb detector

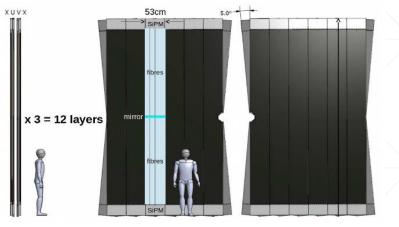

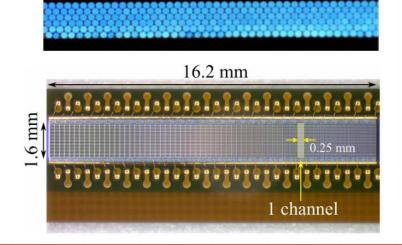

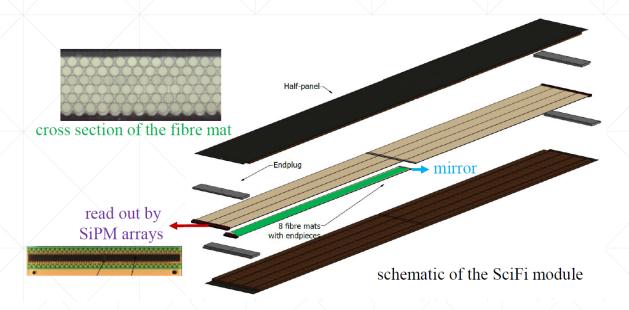

### SciFi – Fibre Mat & Module

- 250µm diameter scintillating fibre wound into a 6-layer 2.4m-long fibre mat

- $\checkmark$  one end equipped with a mirror

- ✓ read out by  $4 \times \text{SiPM}$  arrays

- 8 × fibre mat + honeycomb = sandwich-structure 0.5m × 5m module

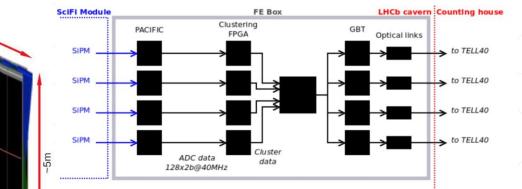

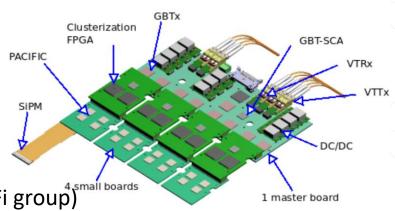

### Sci-Fi readout electronics (FE)

Tracker structure:

- ✓ 3 Tracking Stations

- ✓ 12 detector layers (X-U-V-X, 5°)

- ✓ 144 modules

✤Electronics design:

- ✓ ~340m<sup>2</sup> total active surface

- ✓ 590,000 SiPM channels

- ✓ 12,000 PACIFIC chips needed

- ✓ 2,500 Frontend Electronic Boards

#### ✤LHCb China Group 2016~2018:

- ✓ Co-design Sci-Fi Frontend Electronic Boards

- ✓ Manufacturing all Frontend Boards in China, testing a part

- ✓ Sci-Fi Readout Electronics Quality Assurance System (For chips and boards)

- ✓ Readout Electronics for Detector Performance Evaluation (>20 setups in Sci-Fi group<sup>4</sup>)<sup>sn</sup>

mirror

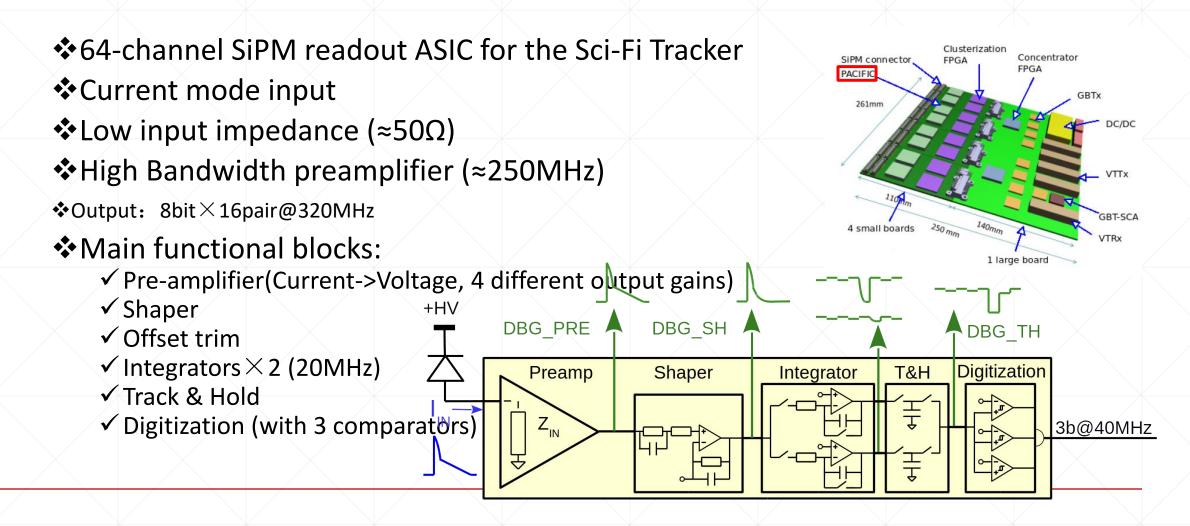

### PACIFIC5

### **PACIFIC Frontend Board**

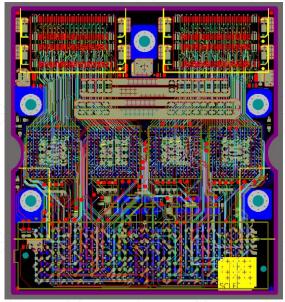

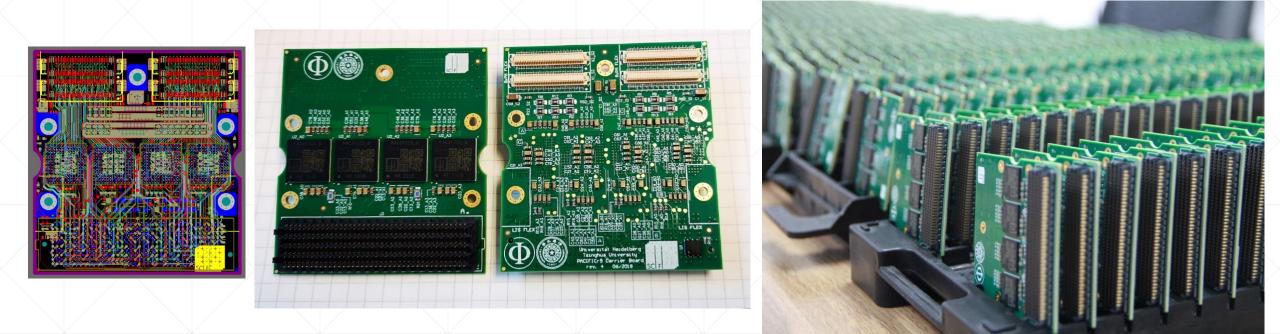

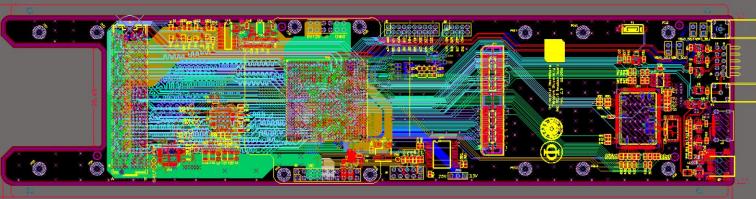

We decided to re-optimize the routing of the PACIFIC Frontend Board

- →  $4 \times \text{PACIFIC ASICs}$  (196-pin BGA packaged)

- 4 × temperature measurement circuits (voltage divider circuits with NTC, 2 for SiPMs, 2 for the ASICs)

- > 4  $\times$  SiPM bias voltage measurement circuits (voltage divider circuits)

- 1 × BoardID IC (DS2401 64-bit unique, factory-lasered silicon serial number, no permanent damage up to 140Gy)

http://radwg.web.cern.ch/RadWG/Pages/showExternal.aspx?GotoUrl=https://twiki.cern.ch/twiki/bin/viewauth/Main/Tullios

<u>PreferredPartList</u>

- $4 \times \text{SiPM}$  flex cable connectors (Hirose DF12(3.0)-80DS-0.5V)

- >  $1 \times FMC$  connector (ASP-134602-01)

re-optimised PACIFIC Frontend Board r4

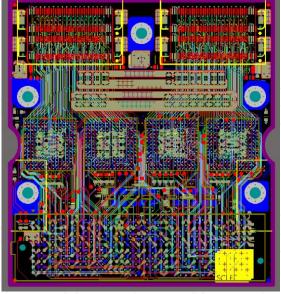

### **Redesign of PACIFIC Frontend Board**

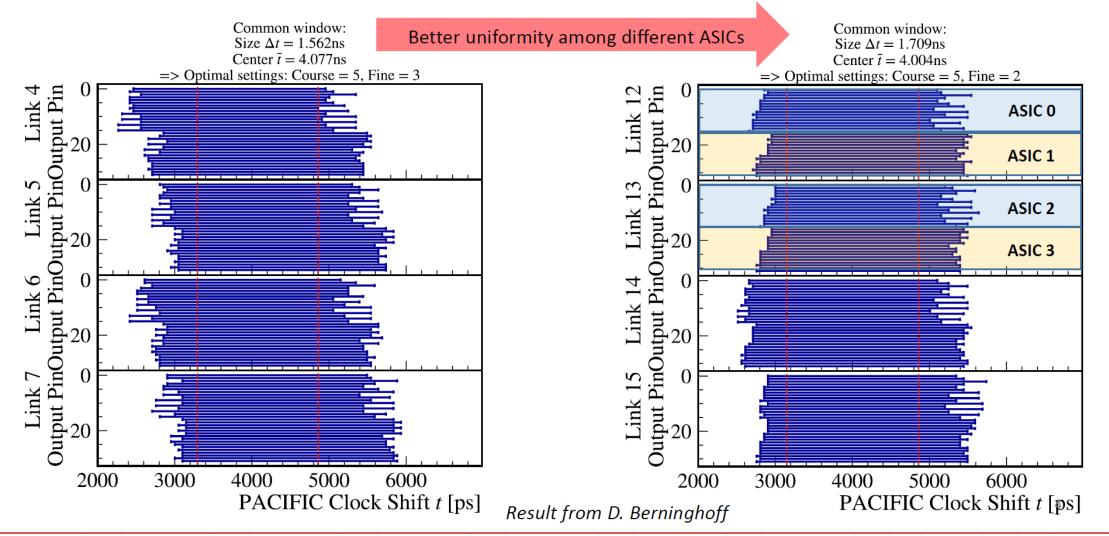

#### We decided to re-optimize the routing of the PACIFIC Frontend Board

- for a higher production yield

- more strict routing constrains, to gain some margin for the sampling window size

- → 4 pairs of PACIFIC Clock lines (CLKIN\_0~3) : routing length match < 1mm

- ▶ 4 SYNC lines (SYNC\_0~3): routing length match < 1 mm

- → 64 pairs of data lines (DATA\_0~3\_X) : routing length match <3mm.

- ➢ well seperate the analog input signals and the output data lines, the CLOCK lines

- ➢ from 8-layers to 14-layers

- Calculate impedance for Halogen Free (TU-862HF), and keep thickness 1.7mm

re-optimised PACIFIC Frontend Board r4

The design has been complete.

For the first 250 PACIFIC Frontend Boards, we will assemble first 10 PCBs, check with the SciFi full electronics (MB+CB) to make sure everything works fine after this optimization.

### **Redesign of PACIFIC Frontend Board**

# **BER test with SciFi FE**

#### **Redesign of PACIFIC Frontend Board & Mass Production**

2018.09 - First 250 PACIFIC Frontend Boards finished ! (for first C-Frame of SciFi)

2019.09 – Finished all 2,300 PACIFIC Frontend Boards !

### First Setup of SciFi C-Frame

#### Test with SiPM + Light Injection System

First Setup of SciFi C-Frame (Sci-Fi milestone of 2018)

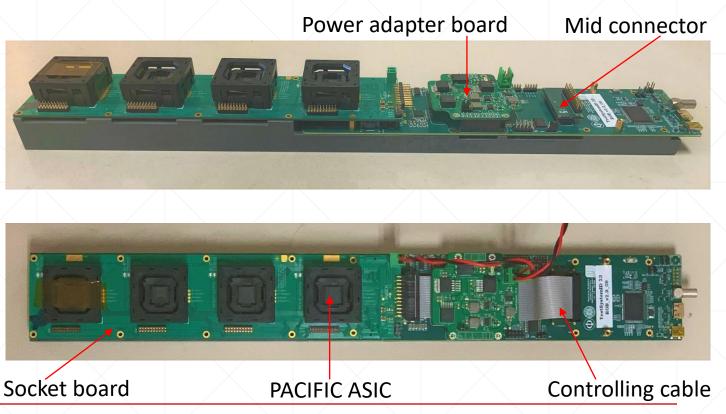

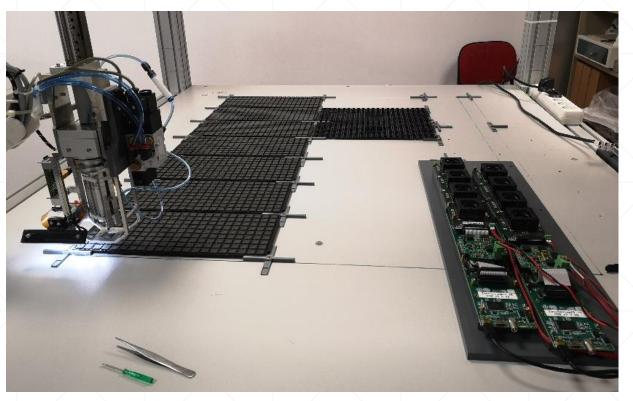

# QA System for PACIFIC chips

Custom designed test DAQ (PACIFICROB): [fully tested, 4 for Heidelberg, 3 for Barcelona, 3 for Valencia]

- ✓ Altera Cyclone FPGA (clock generation, ASIC configuration, data process, sensor readout ...)

- ✓ precision clock conditioner to fine tune the clock for each ASIC

- ✓ (LVDS-SLVS convertor)

- ✓ 8-channel, 12-bit ADC

- ✓ USB interface to PC

#### Socket Board:

- ✓ 4 sockets to nip chips

- $\checkmark$  Connected with FMC & controlling cable

- DC power supply

- ✓ Output 5V/3A at least

#### ✤Linux PC

Robot arm (Barcelona)

# QA System for PACIFIC chips

Custom designed test DAQ (PACIFICROB): [fully tested, 4 for Heidelberg, 3 for Barcelona, 3 for Valencia]

- ✓ Altera Cyclone FPGA (clock generation, ASIC configuration, data process, sensor readout ...)

- ✓ precision clock conditioner to fine tune the clock for each ASIC

- ✓ (LVDS-SLVS convertor)

- ✓ 8-channel, 12-bit ADC

- ✓ USB interface to PC

- Socket Board:

- ✓ 4 sockets to nip chips

- $\checkmark$  Connected with FMC & controlling cable

- DC power supply

- ✓ Output 5V/3A at least

- ✤Linux PC

Robot arm (Barcelona)

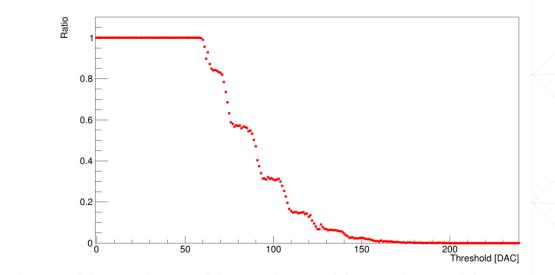

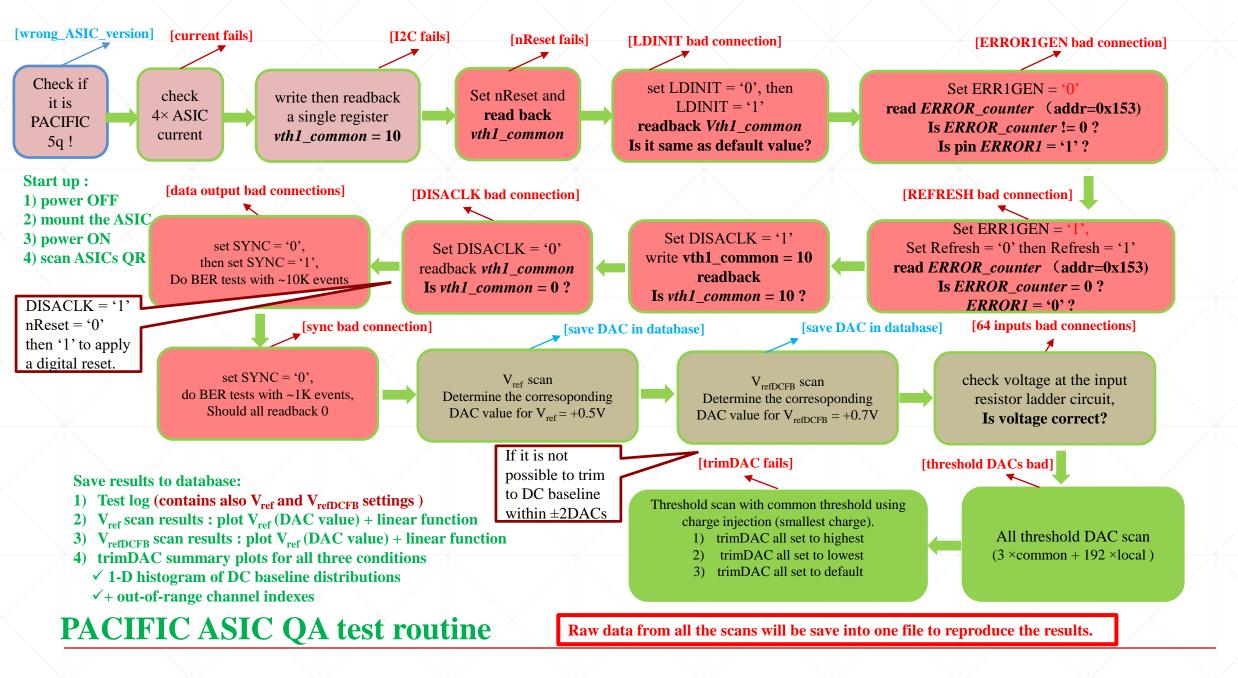

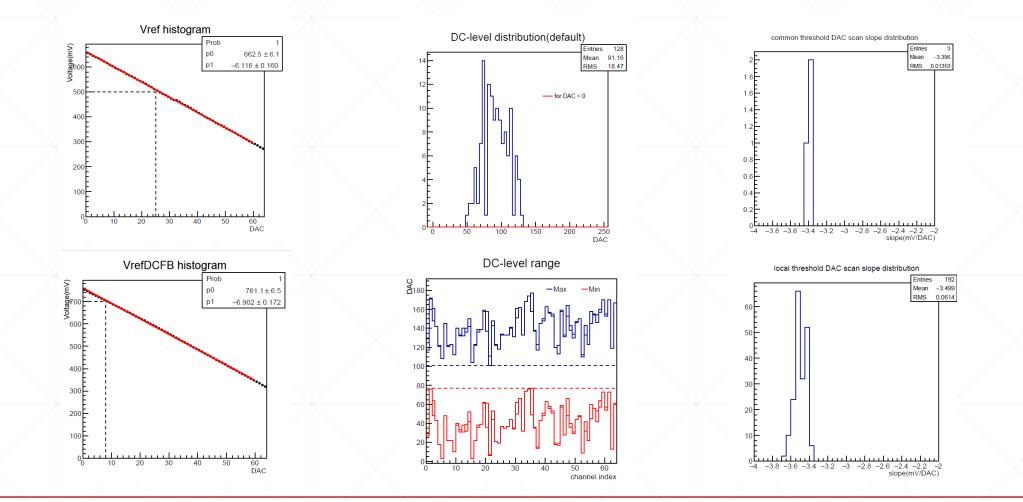

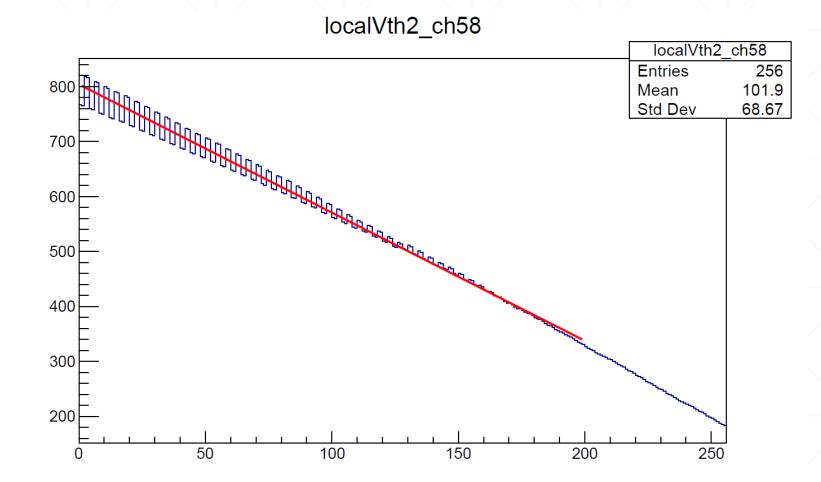

### Main features of test results for one chip

test automatically update result to DB

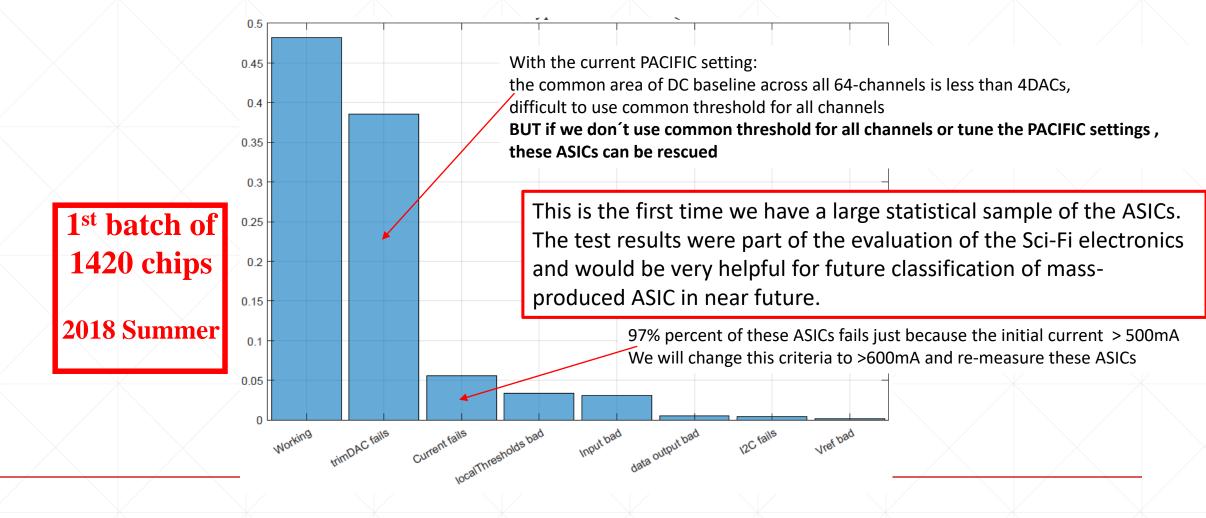

finish all 1<sup>st</sup> batch 1420 PACIFIC5q test

final check the QA test routine

LHCb Production Interface

QA test running : 10 ASICs/run, ~100ASICs/hour

Xiaoxue Han (Logout)

#### All results can be found in Sci-Fi Production DB

| <ul> <li>Readout Box Productions</li> <li>Readout Box Compone</li> </ul>                                   | Find by Ba      | rcode      |                       |            | Search     | ł | nttps                           | ::// | 'scifi.                 | phy     | ysi.                       | uni-ł                         | neidel                       | be   | erg.c | le/d                                                                 | b/prod/                                                                                           | Н                 | lover prev    |

|------------------------------------------------------------------------------------------------------------|-----------------|------------|-----------------------|------------|------------|---|---------------------------------|------|-------------------------|---------|----------------------------|-------------------------------|------------------------------|------|-------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------|---------------|

| PACIFIC ASICs                                                                                              | ins             |            |                       |            |            |   | -                               |      |                         | New PAC | CIFIC ASI                  | IC (total: 141                | 0 <u>CSV</u> , <u>SCSV</u> ) |      | -     |                                                                      | •                                                                                                 |                   |               |

| PACIFIC Boards Readout Box Operation                                                                       |                 | Show Alter |                       |            |            |   |                                 |      |                         |         |                            |                               |                              |      |       |                                                                      |                                                                                                   |                   |               |

| <ul> <li>Quaroses</li> <li>QuarosSystems</li> </ul>                                                        | Inventory       |            |                       |            |            |   | Dimensions<br>[mm x mm x<br>mm] |      | Material<br>composition | Comment | Initial<br>current<br>[mA] | Configured<br>current<br>[mA] |                              | Vref |       | Summary<br>report<br>[.pdf]                                          | Raw data [.root]                                                                                  | PACIFIC<br>Boards |               |

| SiPMs for Quaroses<br>Adapter boards                                                                       | EPA00009        | PI         | PACIFIC5_Q-<br>Adummy | 2018-05-26 | 2018-06-07 |   |                                 |      |                         |         | 0                          | 0                             | I2C fails                    | 0    | 0     | -                                                                    | rawData AsicQA testsystem8 ASICID PACIFIC5 Q-<br>Adummyroot<br>2018-06-07 19:48:46 by Xiaoxue Han | Q                 | Modify        |

| Spiroc FEs<br>Power supply units<br>USBboards<br>Laser mezzanines<br>Spiroc ASICs<br>Upload Quaros fileses | <u>EPA00010</u> |            | PACIFIC5_Q-<br>A2104  | 2018-05-26 | 2018-06-07 |   |                                 |      |                         |         | 434.4                      | 511.8                         | trimDAC fails                | 27   | 6     | PACIFIC5 Q-<br>A2104.pdf<br>2018-08-07<br>20:21:10 by<br>Xiaoxue Han | rawData AsicQA testayatem8 ASICID PACIFIC5 Q-<br>A2104.rodi<br>2018-96-07 19 48 50 by Xiackue Han | ٥                 | <u>Modify</u> |

|                                                                                                            | EPA00011        | PI         | PACIFIC5_Q-<br>A2105  | 2018-05-26 | 2018-06-07 |   |                                 |      |                         |         | 411                        | 511.8                         | Working                      | 25   | 9     | PACIFIC5 Q-<br>A2105.pdf<br>2018-08-07<br>19:48:55 by<br>Xiaoxue Han | rawData AsicOA testsystem8 ASICID PACIFIC5 Q-<br>A2105.0001<br>2018-06-07 19 48:58 by Xiaoxue Han | Q                 | <u>Modify</u> |

|                                                                                                            | EPA00012        | PI         | PACIFIC5_Q-<br>A2106  | 2018-05-26 | 2018-06-07 |   |                                 |      |                         |         | 458.8                      | 515                           | Working                      | 29   | 9     | PACIFIC5 Q<br>A2106.pdf<br>2018-06-07<br>19:49:02 by<br>Xiaoxue Han  | rawData AsicOA testsystem® ASICID PACIFICS Q-<br>A2105.rogt<br>2018-06-07 19:49:05 by Xiaoxue Han | ٥                 | Modify        |

### QA test for 1<sup>st</sup> batch of packaged PACIFIC5q

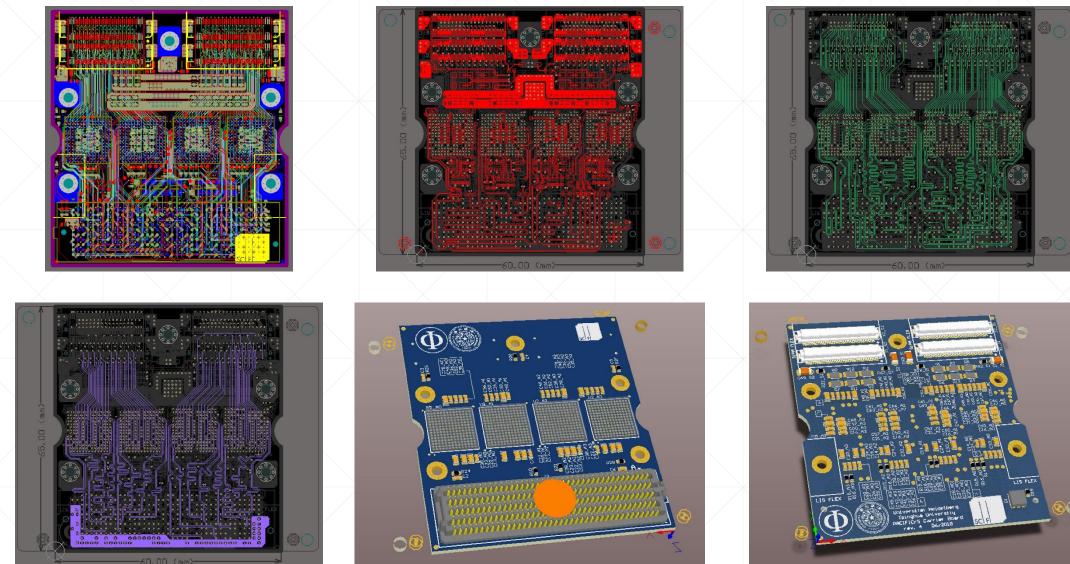

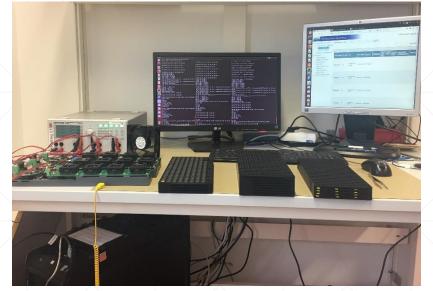

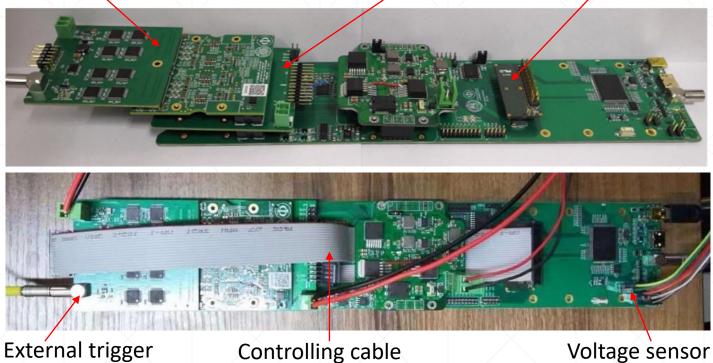

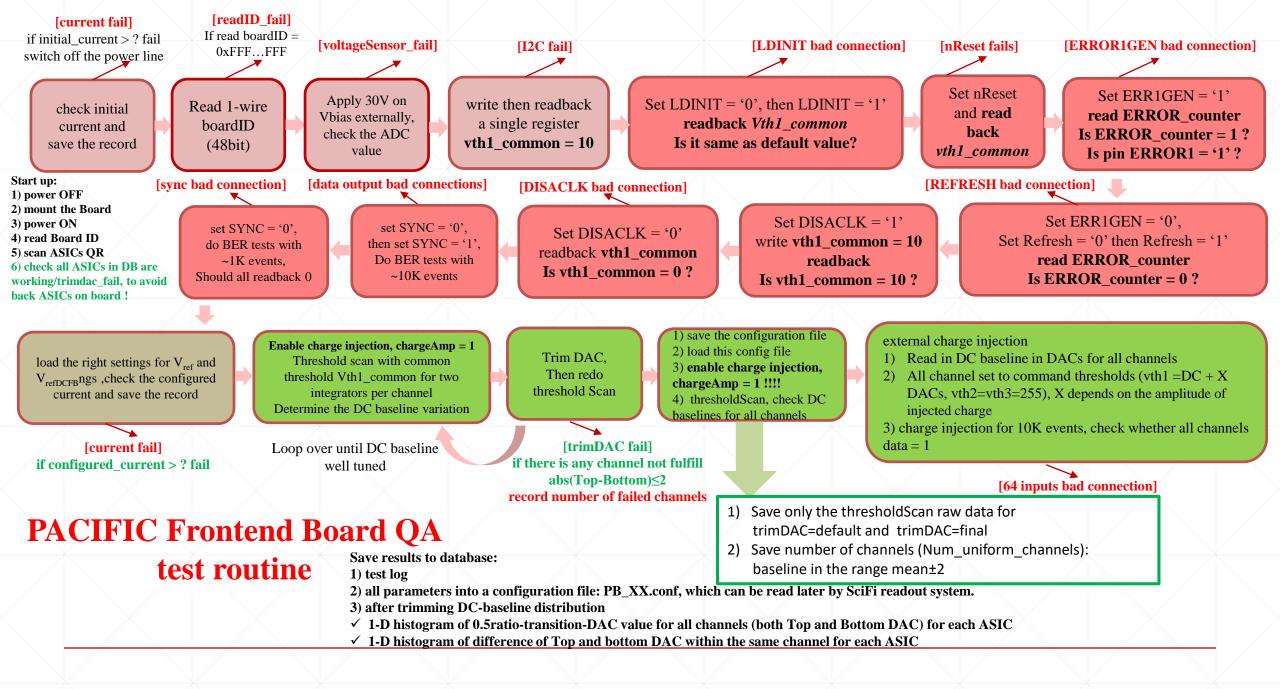

## QA System for Frontend Boards

Custom designed test DAQ (PACIFICROB): [fully tested, 3 for Heidelberg (delivered), 3 for Barcelona, 3 for Valencia]

- ✓ Altera Cyclone FPGA (clock generation, ASIC configuration, data process, sensor readout ...)

- ✓ precise clock conditioner to fine tune the clock for each ASIC

- ✓ LVDS-SLVS convertor

- ✓ 8-channel, 12-bit ADC

- ✓ USB interface to PC

- FMC connector intermedia board:

- ✓ Simple pin-to-pin adapter PCBs

- ✓ To avoid broken FMC connectors

- Charge injection board

- DC power supply

- ✓ Output 5V/3A at least

- Arbitrary waveform generatorLinux PC

### QA System for Frontend Boards

Custom designed test DAQ (PACIFICROB): [fully tested, 3 for Heidelberg (delivered), 3 for Barcelona, 3 for Valencia]

- ✓ Altera Cyclone FPGA (clock generation, ASIC configuration, data process, sensor readout ...)

- ✓ precision clock conditioner to fine tune the clock for each ASIC

✓ (IVDS\_SIVS convertor)

External charge injection board

- ✓ (LVDS-SLVS convertor)

- ✓ 8-channel, 12-bit ADC

- ✓ USB interface to PC

- FMC connector intermedia board:

- ✓ Simple pin-to-pin adapter PCBs

- ✓ To avoid broken FMC connectors

- Charge injection board

#### DC power supply

- ✓ Output 5V/3A at least

- Arbitrary waveform generator Linux PC

FMC adapter board Mid connector

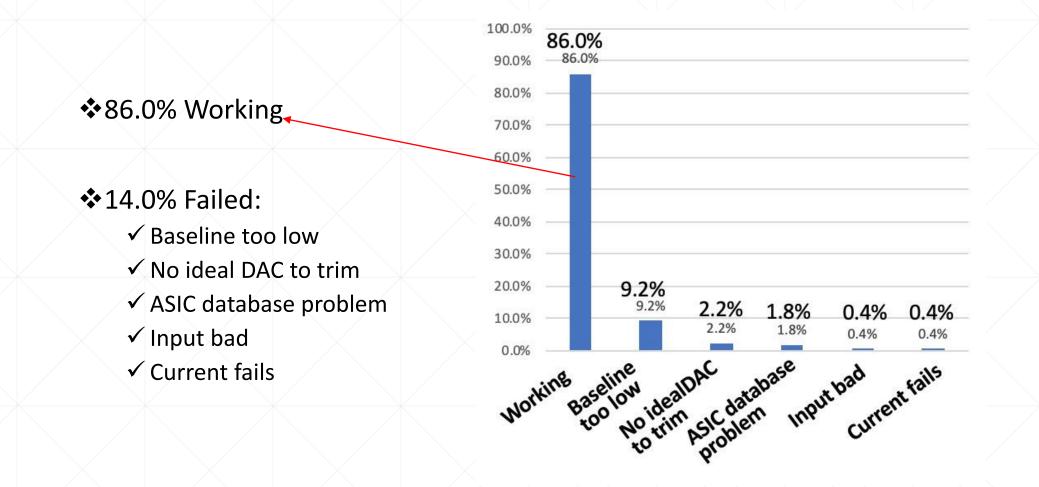

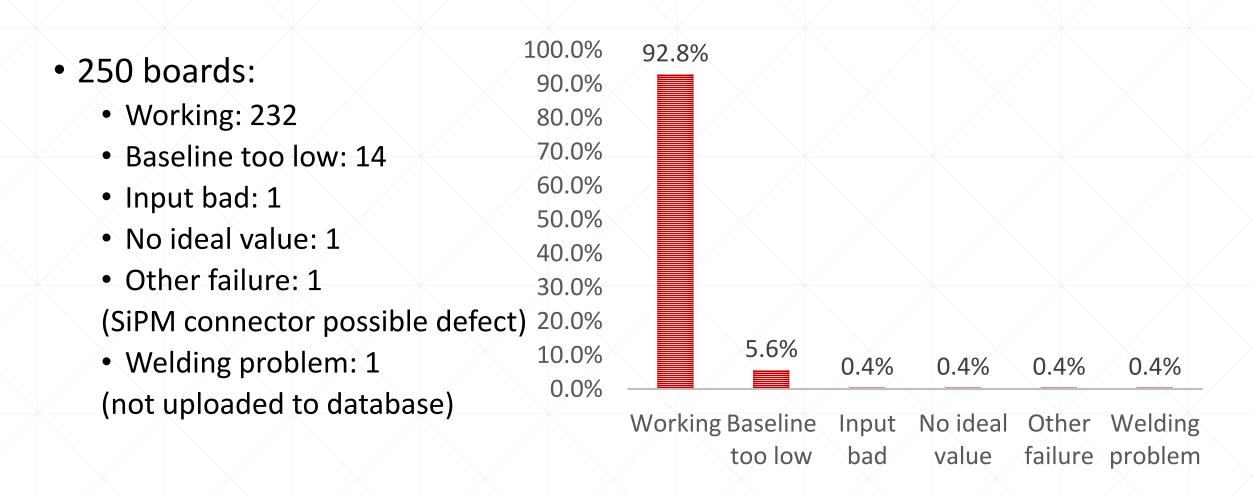

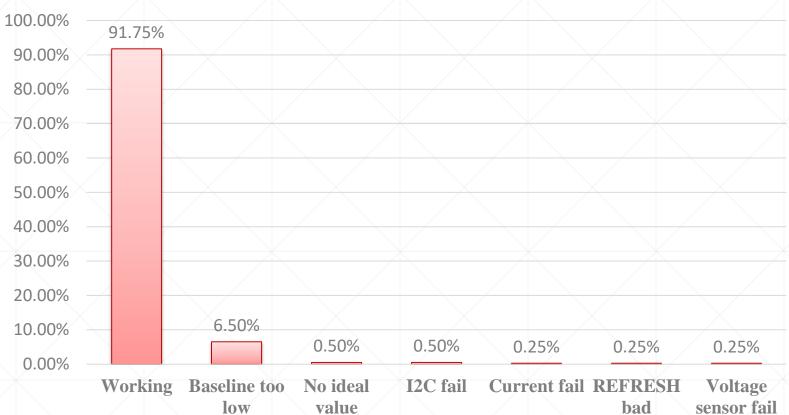

### First 250 PACIFIC Frontend Boards Tested

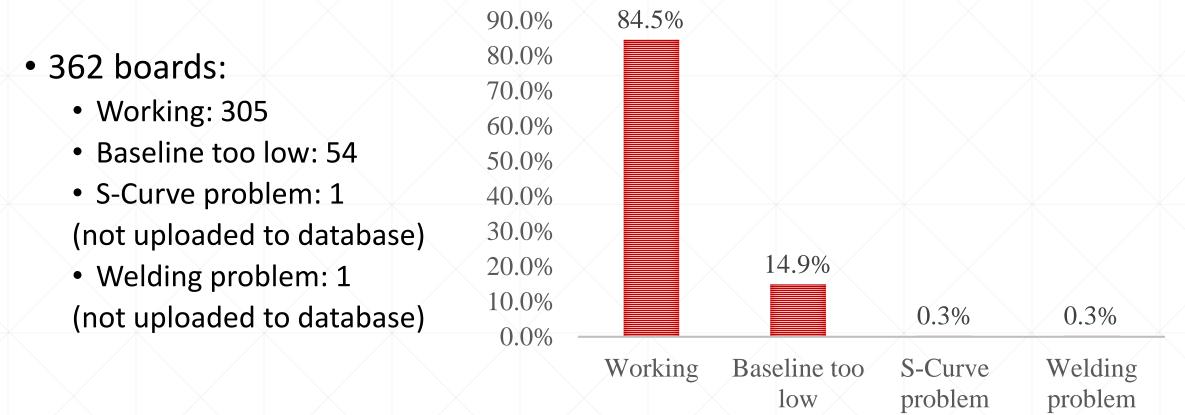

### Updated test result for 2<sup>nd</sup> batch in Tsinghua

Solved the current fail problem and retested several boards

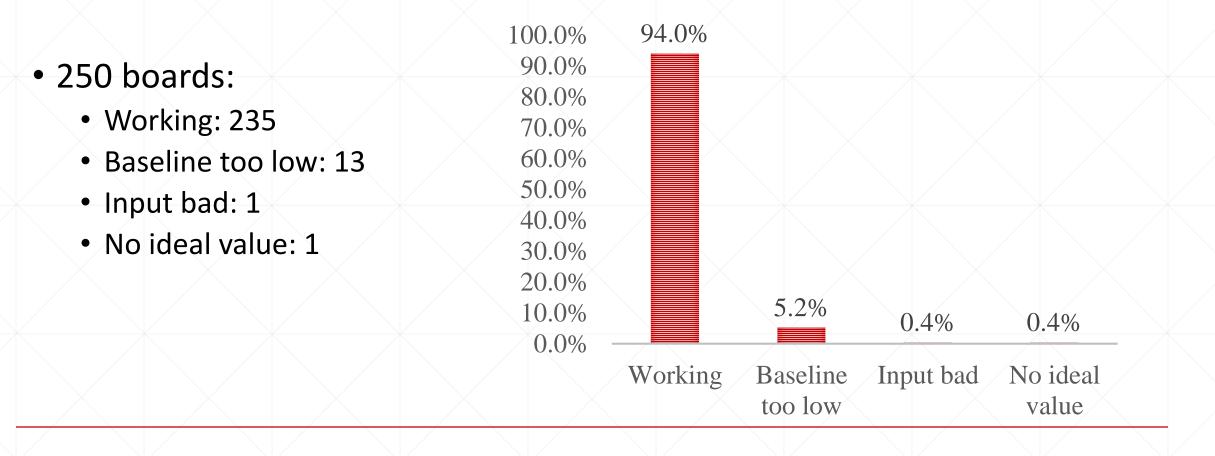

### Updated test result for 3<sup>rd</sup> batch in Tsinghua

Solved the current fail problem and retested several boards

### Test result for 4<sup>th</sup> batch in Tsinghua

### Test result of 5<sup>th</sup> batch in Tsinghua: Total

- 400 boards:

- Working: 367

- Baseline too low: 26

- 12C fail: 2

- No ideal value: 2

- Current fail: 1

- REFRESH bad: 1

- Voltage sensor fail: 1

### Main features of test results for one chip

# LHCb Upgrade I: SciFi

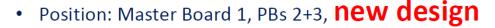

#### Production:

| PACIFIC   | Chip      | 100% produced and tested                                                                                                                                                      |

|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PACIFIC   | Board     | 100% produced and tested                                                                                                                                                      |

| Cluster B | oard      | 100% prodcued and tested                                                                                                                                                      |

| Master B  | oard      | Preseries 50 MBs: ok<br><u>Main production (570 boards):</u><br>Batch 1: 96 MBs in July<br>Batch 2: 104 MBs in Aug<br>Batch 3: 100 MBs in Sep<br>Next batches: 08 Nov, 06 Jan |

| Mechanio  | cal Parts | 100% produced                                                                                                                                                                 |

| $\sim$          |                                                                                                        |

|-----------------|--------------------------------------------------------------------------------------------------------|

| Front-end boxes | Preseries (23) ready $\rightarrow$ frame1<br>Batch 1: 30 boards at CERN<br>Batch 2: expected this week |

|                 | Batch 2: expected this week                                                                            |

|                 | Next batches: 30 FEBs/3 weeks                                                                          |

FEB finishing determined by MB schedule: Significant delays, however in shadow of delays of C-frames

Very detailed test of FEBs at CERN, progressing very well (Massa + students).

Congratulations to

From SciFi IB

- <u>Tsinghua,</u> Valencia, HD

- Clermont-Ferrand

## LHCb SciFi China Group

# LHCb Upgrade I: SciFi (LHCb China Group)

- SciFi: 524,000 SiPM Channels

- PACIFIC 64 channel SiPM readout ASIC

- LHCb SciFi China Group :

- Co-design the PACIFIC Board (with Heidelberg)

- Manufacture all 2,300 PACIFIC Boards (Finished in 2019)

- Test 1/2 of the PACIFIC Boards (another ½ @Valencia)

- Quality Assurance System for PACIFIC chip selection

- (6 setups @Tsinghua, Barcelona and Heidelberg)

- Quality Assurance System for PACIFIC Board

- (5 @Tsinghua, Valencia and Heidelberg)

- Software: Build new sequence for SciFi specific processing of Testbeam data.

- Commissioning in 2020 .....

# Thank you!

Questions?

第五届中国LHC物理工作会议

References:

.

. . . . . .

- https://cds.cern.ch/record/2630472/files/passalevaichep%2007.07.pdf

- <u>https://cds.cern.ch/record/2650584/files/181206\_Kruger.pdf</u>

- <u>https://cds.cern.ch/record/2648754/files/grauges-LHCb-</u> <u>NagoyaHfNPFP.pdf</u>