# sTGC R&D at SDU for STAR ☆ Forward Upgrade

# Chi Yang Shandong University

# To Use sTGC

### For forward upgrade, we need:

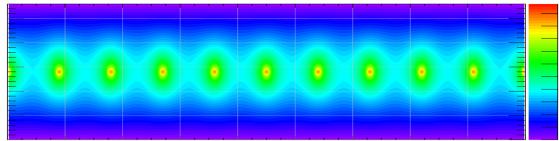

Tracking points in STAR x-y plane

Position sensitive (100-200um)

Low cost

Large coverage

Relative mature technique

### -> small strip Thin Gap Chamber

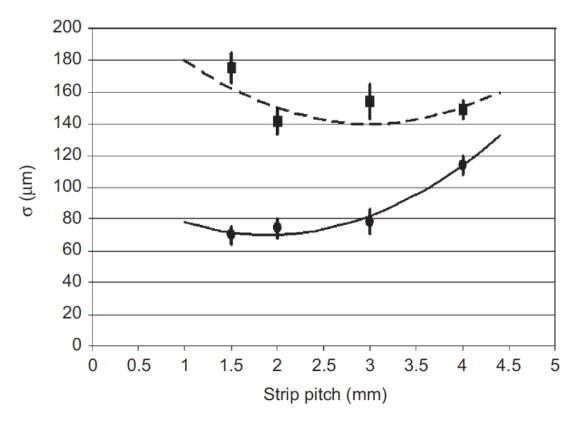

**Fig. 6.** Average position resolution in HV region 2.9–3.2 kV: for the angle region of  $0-10^{\circ}$  (points, solid line) and  $20-30^{\circ}$  (squares, dashed line) as a function of strip pitch. The lines are just to guide the eye.

Developed by ATLAS group: V. Smakhtin et al., NIM.A, 598 (2009) 196–200 A. Abusleme et al., NIM.A, 817(2016) 85–92

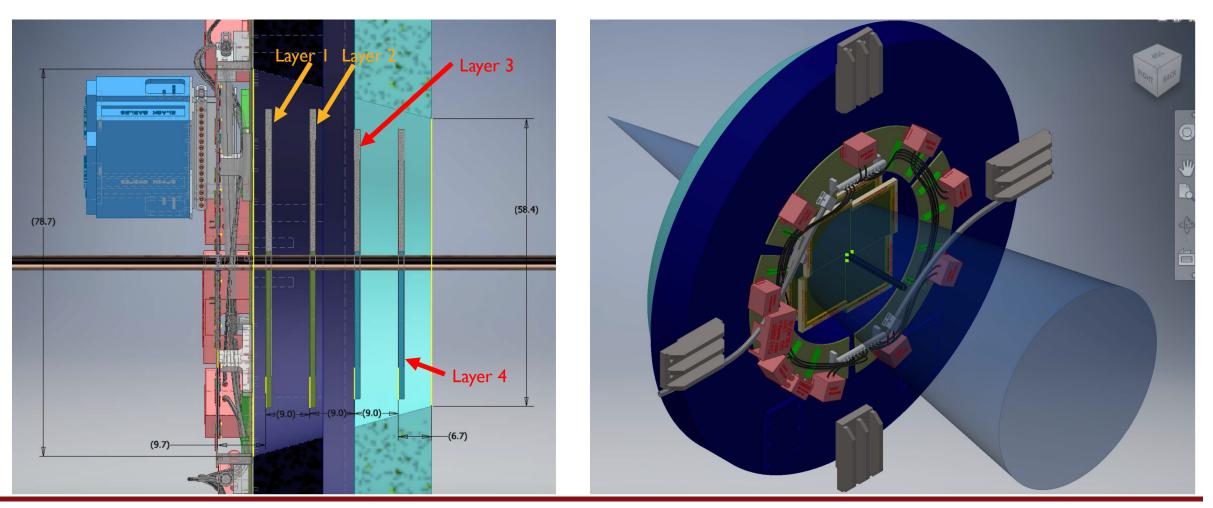

# **sTGC Geometry**

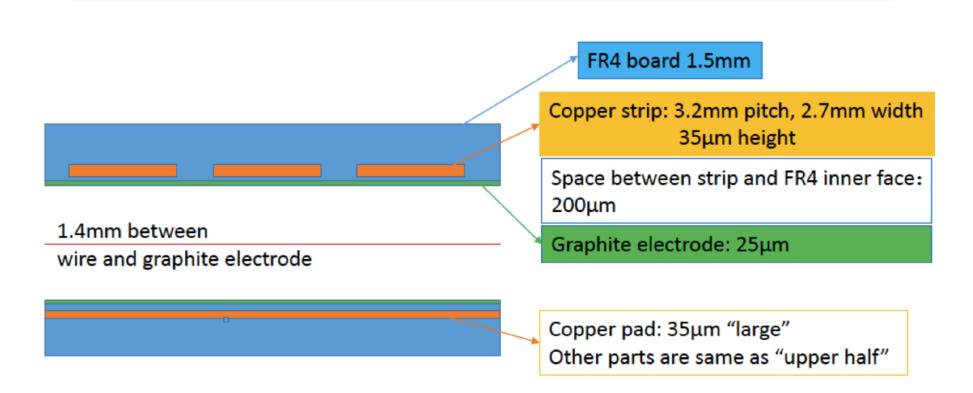

### sTGC layout-side-view

Wire: Φ50μm Au-plate tungsten wire, 1.8mm pitch Working gas: 45% n-pentane + 55% CO<sub>2</sub> Honeycomb paper for mechanic support outside of the layer or in between two layers

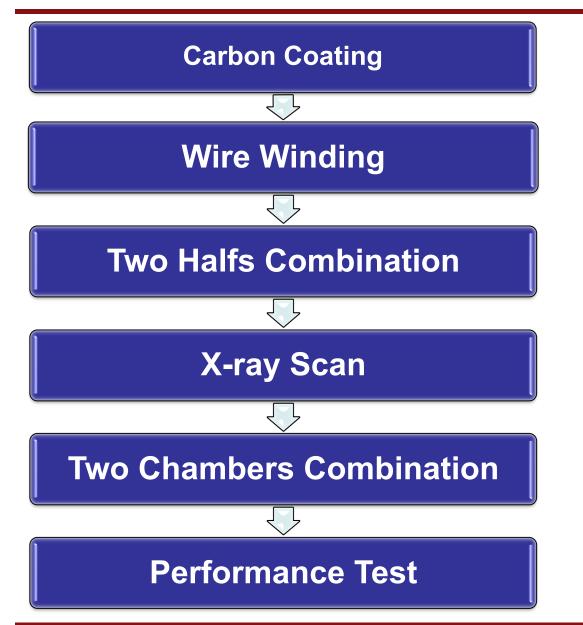

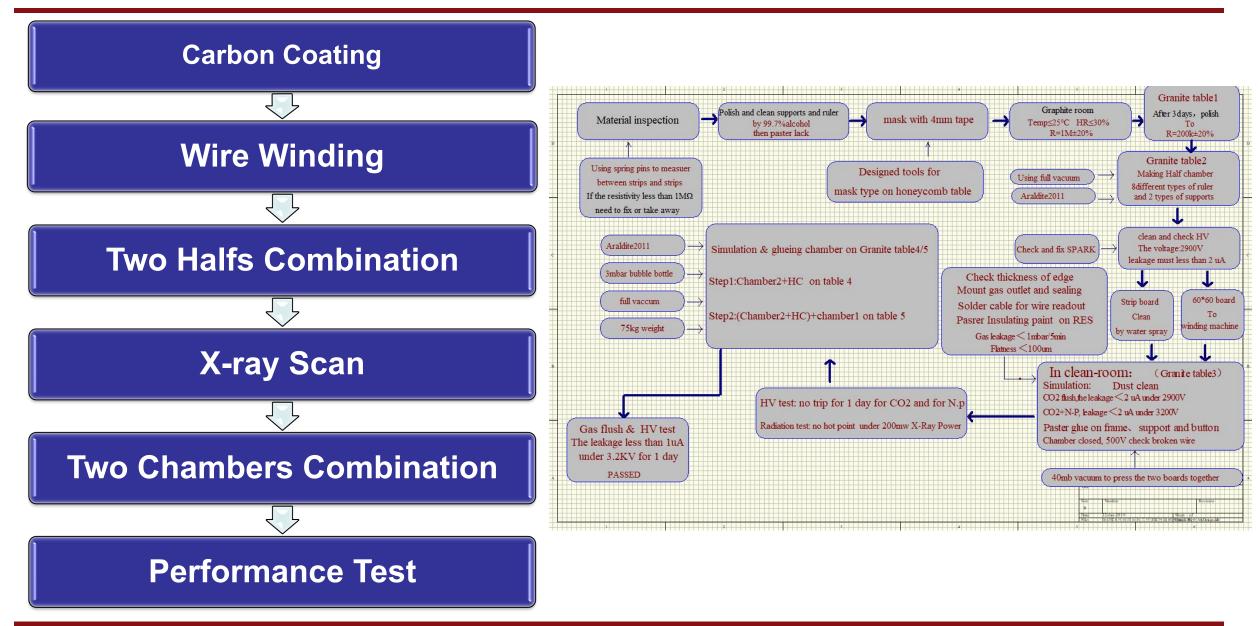

### **sTGC Production Procedure**

Same clean room as iTPC production

Now shared with ATLAS sTGC group

### **sTGC Production Procedure**

### **Graphite Spraying**

SDU ALTAS group have a automatic graphite sprayer

PCBs can be sprayed together

#### Automatic graphite sprayer

### **Surface Polishing**

Polish to surface resistance:  $\sim 200 k\Omega/2.5 cm^2$

Measure -> Polish -> Measure .....

After spraying

#### **Before polishing**

Polishing

Measuring

# Wire Mounts and Supporting Structure Installation

#### **Tooling for supporting structure position constrain**

### **A Wire Plane with Wires**

Ready to be bonded to the PPPCB half to build a chamber

### **Wire Winding**

- $\checkmark\,$  Wires on the side wire mounts of the PCB base

- $\checkmark\,$  Wire tension and pitch are kept by the winding machine

- $\checkmark\,$  Use ATLAS sTGC winding machine

- $\checkmark\,$  Wires are soldered on the wire mounts after winding

- $\checkmark\,$  4 or 8 wire planes can be winded together

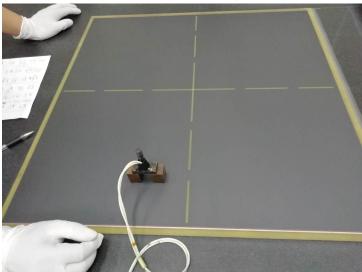

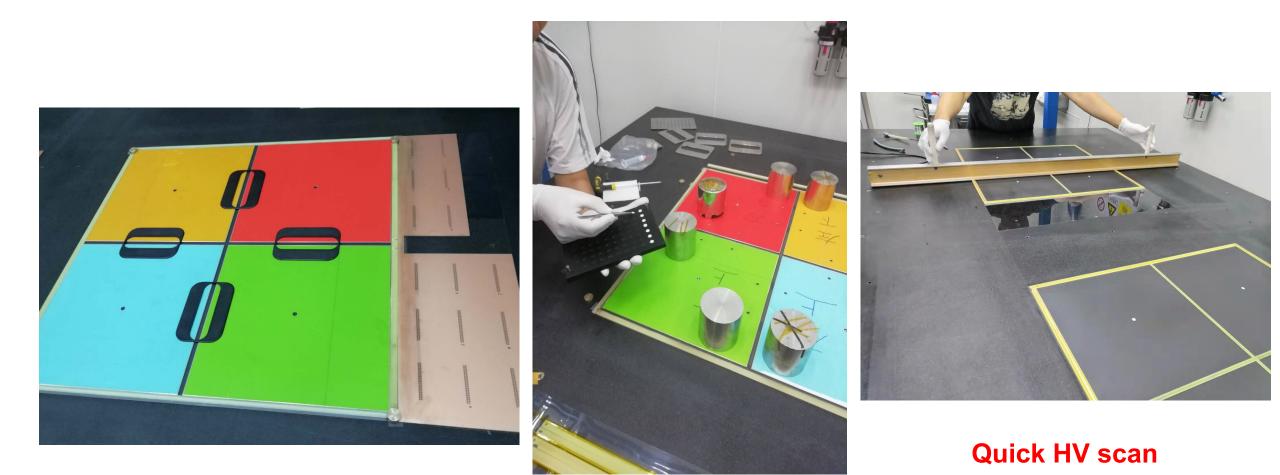

### **Combine the upper and lower half**

#### Vacuum pumping frame on granite table

#### Two halfs combining rehearsal

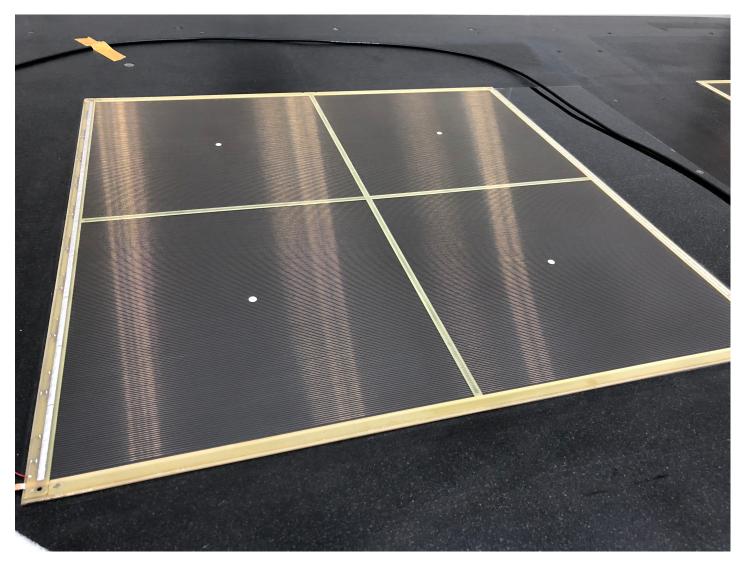

### **Design of the Small Prototype Module**

✓ Similar geometry ATLAS sTGC

---- side view

- ✓ Use strip layer instead of pad layer

- ---- same upper and lower layers

- ✓ Use current ATLAS wire mount and support material

---- need machining

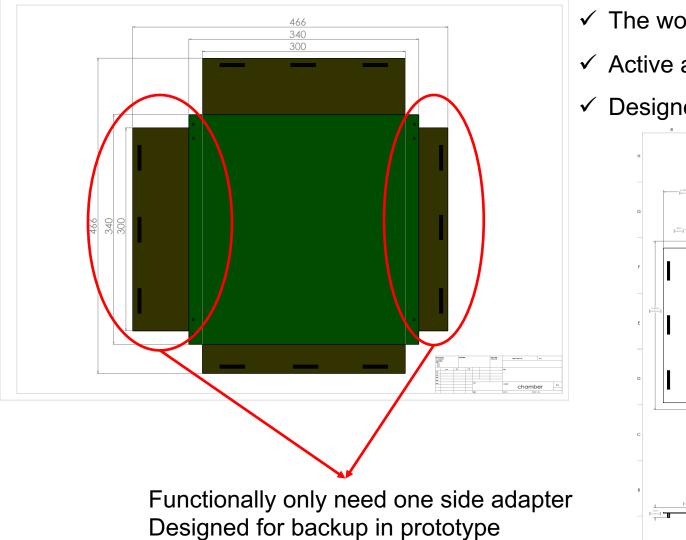

✓ Adapters are designed for both upper and lower pad planes

---- can read the position perpendicular to wire if needed

# **Design of the Small Prototype Module**

- ✓ The work started from Jan.2018

- ✓ Active area is 30cm X 30cm

- ✓ Designed for STAR TPX electronics

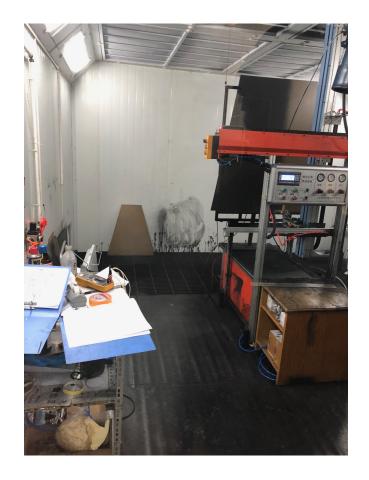

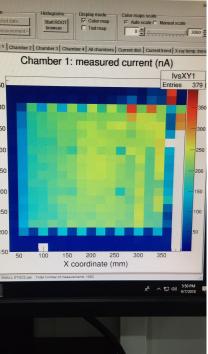

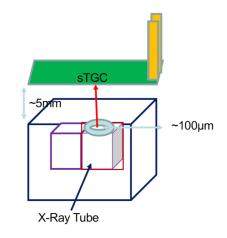

### HV Burn-in and X-ray radiation test

- ✓ Flowing 45% n-pentane and 55%  $co_2$

- ✓ Ramping up to 3200V

- ✓ Track the leakage current

- ✓ No spark observed

#### 2D X-ray scan platform

Step by step scan (2cm/step) Track the leakage current

Due to the previous sTGC experience, seen from the leakage current distribution, the flatness is about 50 micros.

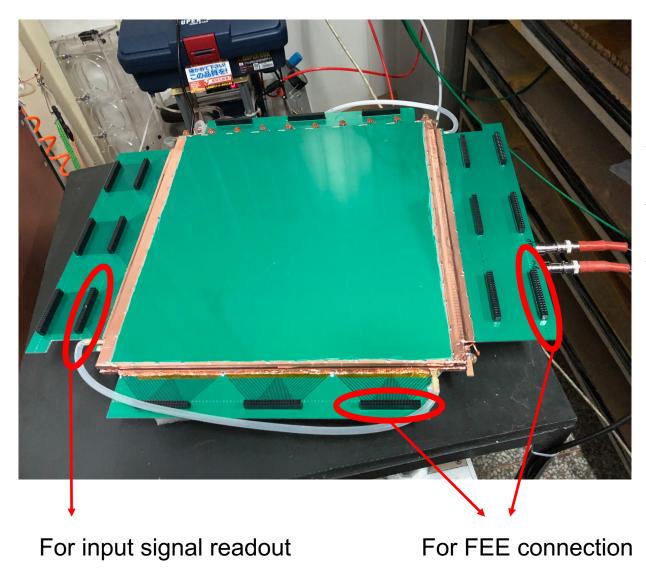

### **Finalized Small Prototype Module**

#### ✓ 2D readout

- $\checkmark\,$  Have input signal readout port for test

- ✓ Need 3 FEEs for 94 channels per layer

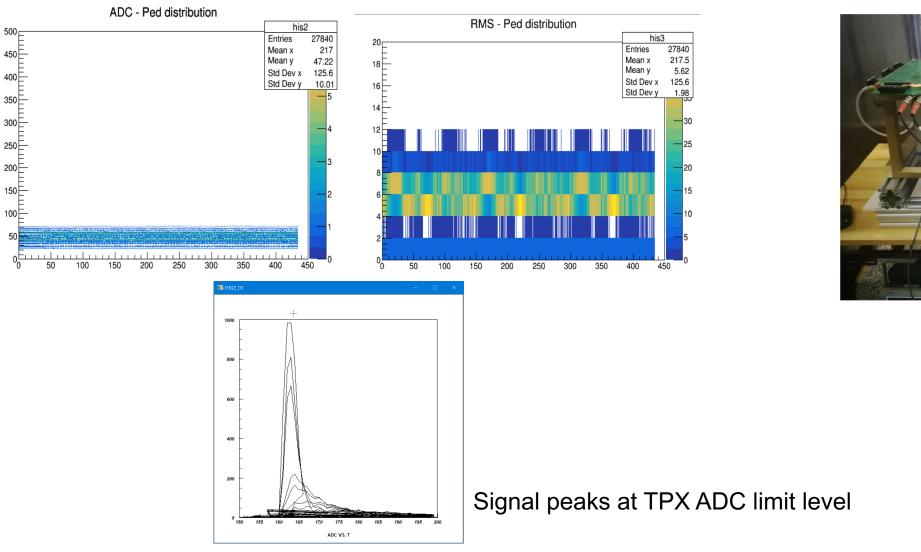

# **Test Results with TPX Electronics at SDU**

#### • RMS ~ 5 compared to 1-2 intrinsic value, not low but acceptable

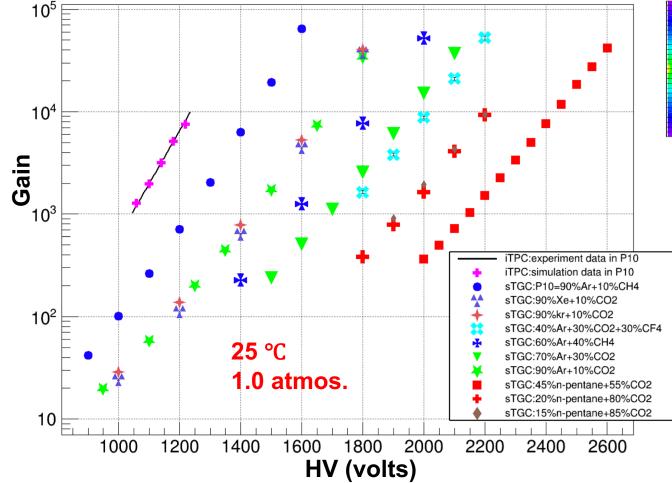

## Garfield++ Simulation on sTGC Gain

#### Simulation is consistent with the measurement for iTPC

F. Shen et al., NIM.A, 896 (2018) 90–95

Need at least one experimental curve to constrain for sTGC

To provide references for different gas options: N-pentane+CO<sub>2</sub> Ar+CH<sub>4</sub> Ar+CO<sub>2</sub> Xe+CO<sub>2</sub> Kr+CO<sub>2</sub> Ar+CO<sub>2</sub> Ar+CO<sub>2</sub>

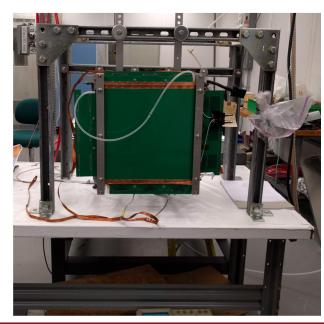

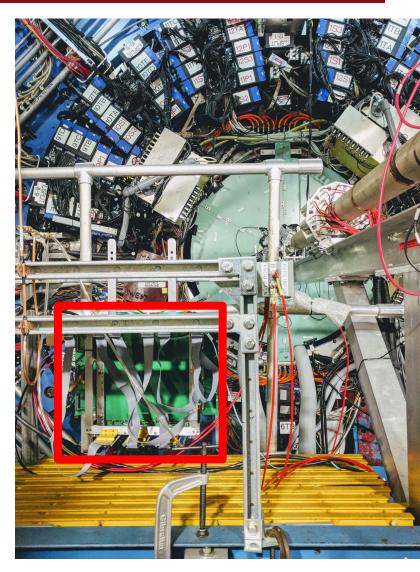

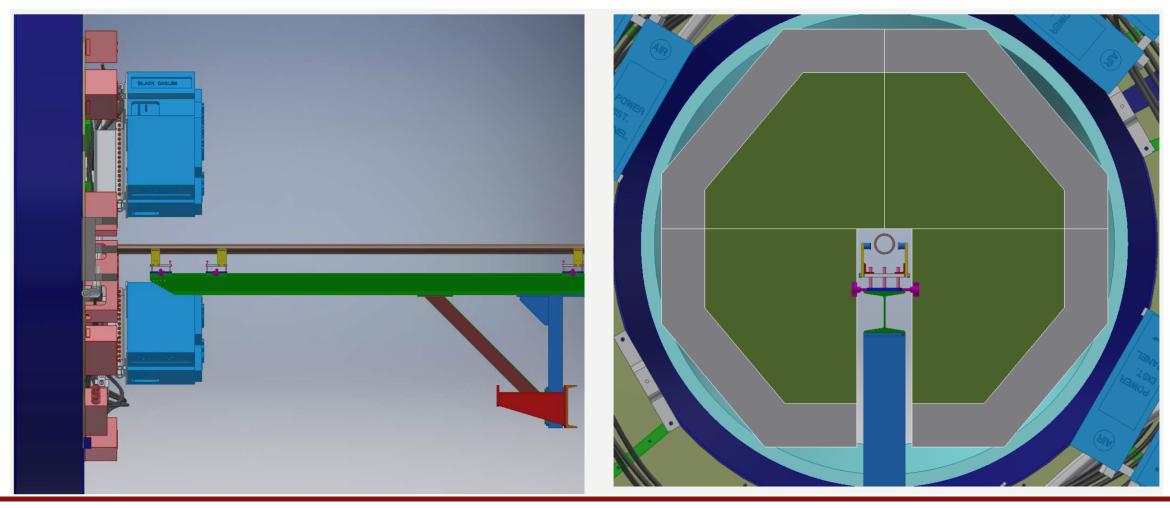

# **Small Prototype at STAR**

- ✓ 30x30 cm prototype delivered to BNL in January 2019

- ✓ Module tested in test-stand using cosmic rays + scintillator pads for trigger

- Connected to STAR Data Acquisition system first test data being analyzed now

- ✓ Installed in STAR on June 5, 2019

- Prototype in STAR Clean Room

#### On the Mounting Structure

On STAR in Run19

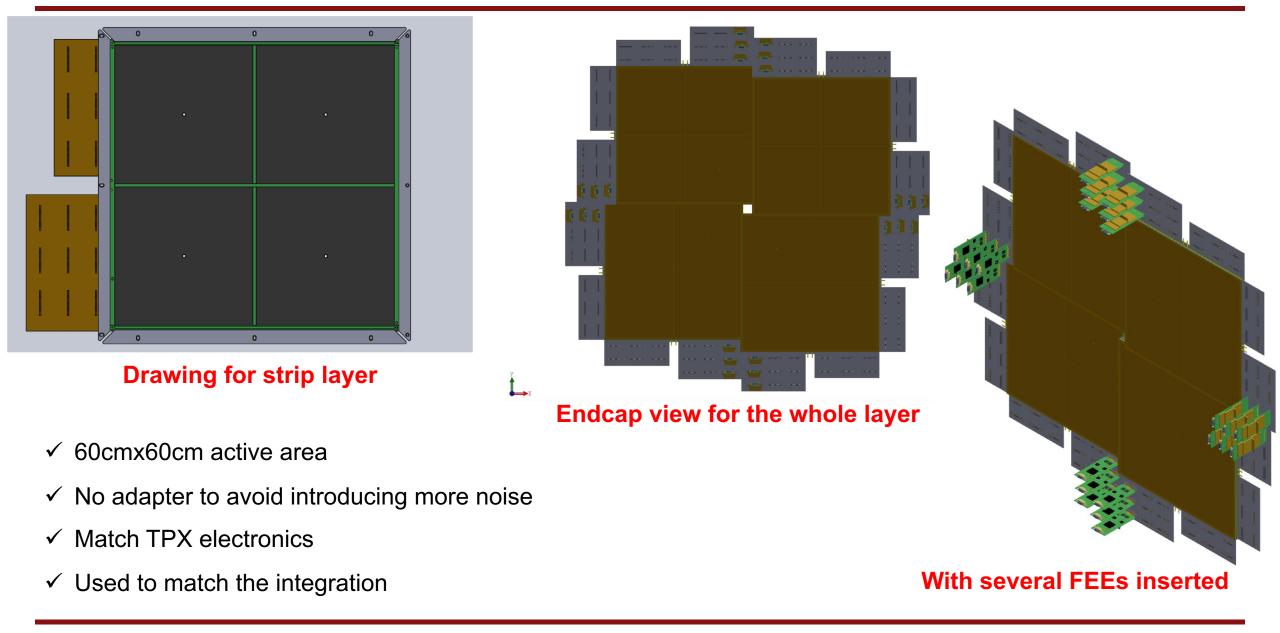

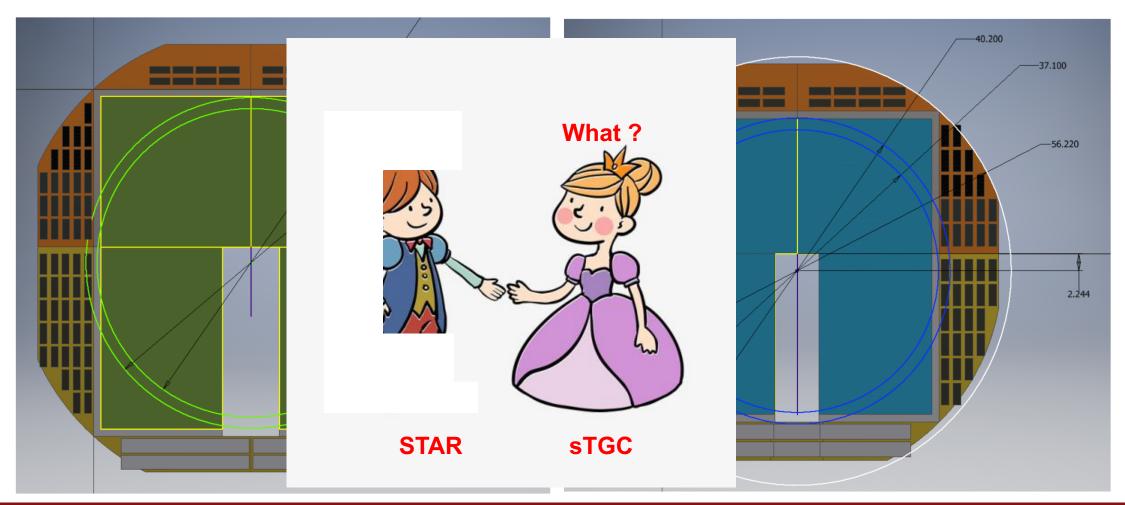

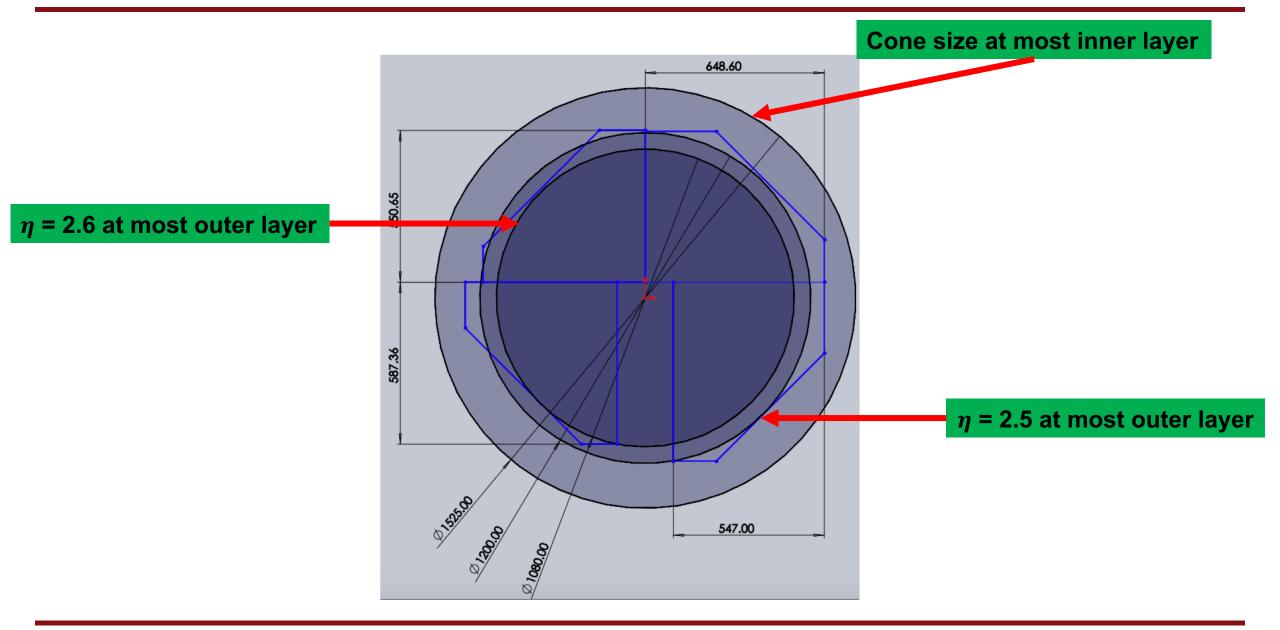

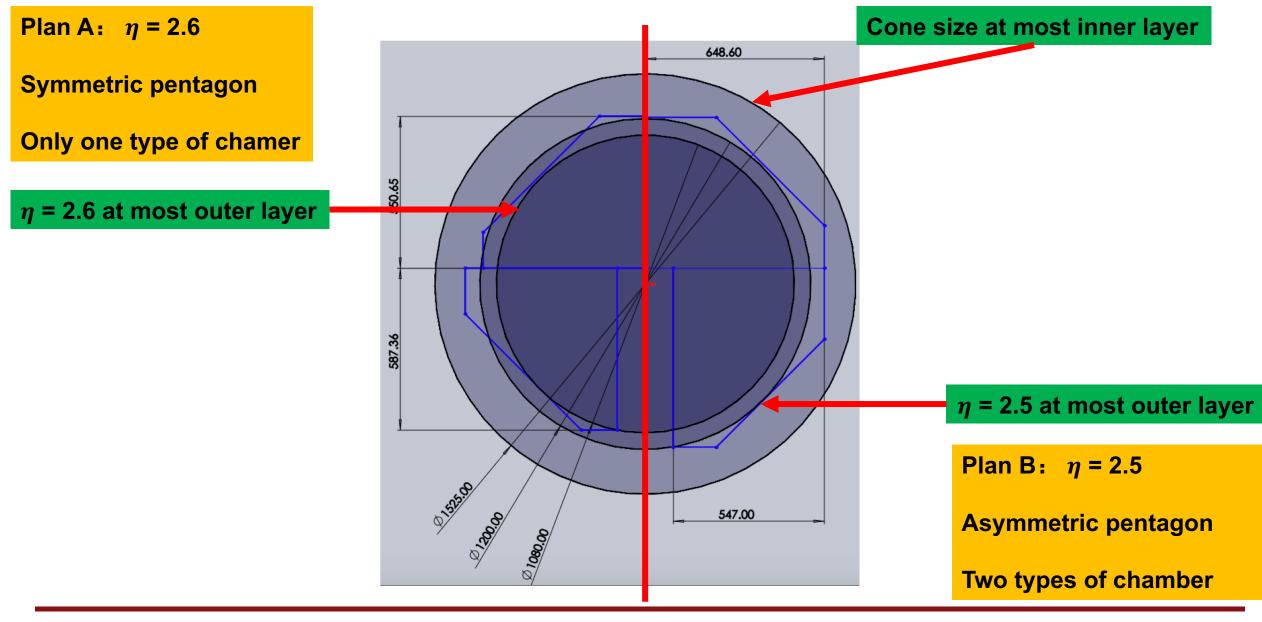

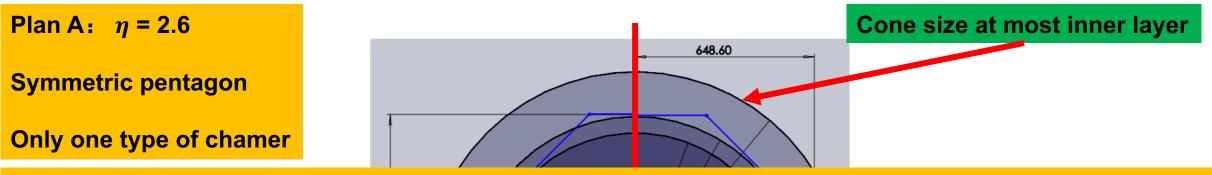

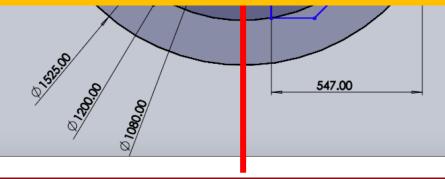

### **Full Size Prototype**

• Used to be a happy story 60cm\*60cm active square plus electronics

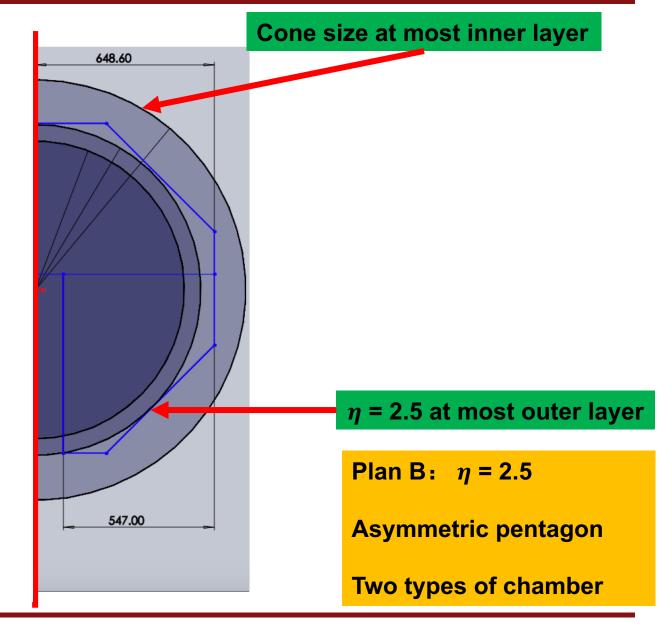

- The size should be limited by the cone size

- Need at least two different sizes for inner and outer layers

- The size should be limited by the cone size

- Need at least two different sizes for inner and outer layers

QCD物理暨国家自然科学基金重大项目交流会, 威海, 杨驰

- There needs to be a gap for lifting if TPC needs to be repaired

- At least need 6 different types of chambers?

- There needs to be a gap for lifting if TPC needs to be repaired

- At least need 6 different types of chambers?

## **Electronics**

Planned to use STAR TPX electronics *iTPC TPX electronics was retired after upgrade* But the spacing usage for TPX electronics is large Very hard to put in the cone size together with the detector

Now considering the ATLAS sTGC electronics using VMM chips 28cmx8cm for 512 channels, including triggering part which is not need for STAR The boards are designed by USTC group

#### ATLAS NSW sFEB

#### ALTAS NSW pFEB

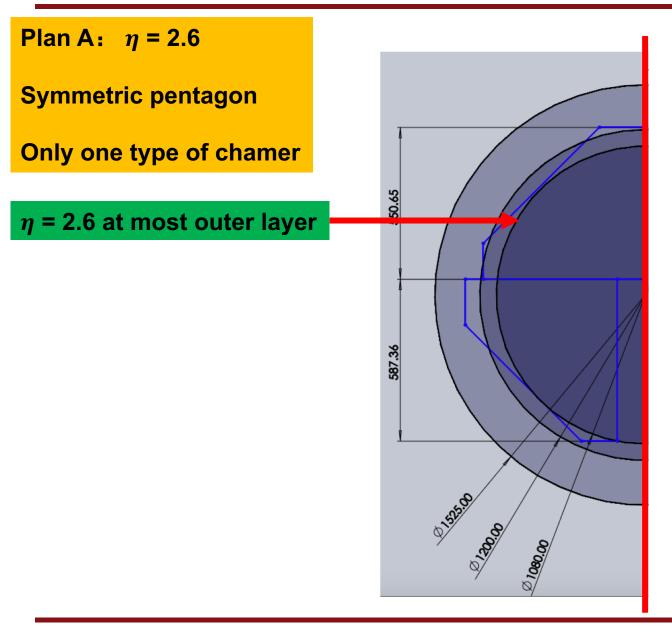

✓ Still need further discussion with the engineers for the pentagon shape feasibility

With this design, the tooling and the final designation can be significantly simplified which is important for mass production

✓ Need to be considered together with the electronics and supporting structure

Plan B: η = 2.5

Asymmetric pentagon

Two types of chamber

# Summary

**Small sTGC prototype** (30cmx30cm) has been designed and **built in SDU**. Preliminary test has been done and results are promising.

The small module was **installed at STAR in Run19**. Data are in studying.

Full size prototype (60cmx60cm) is in building.

Mass production procedure is under developing and improving.

**New pentagon shape design** for mass production is under discussion. Need to use ATLAS VMM chips for readout electronics.

Future plan:

- Detailed performance test for full size prototype (position resolution, efficiency)

- Work together with integration group and electronics group for final design