# Full size pixel chip for high-rate CEPC Vertex Detector

Wei Wei

On behalf of the CEPC MOST2 Vertex detector

design team

CEPC MOST2 Annual Meeting 2019-4-29

### **Outline**

- Motivation of the MOST2 Vertex detector design

- Specification

- Limitation of the existing CMOS sensors towards the highrate CEPC Vertex Detector

- Key improvement for fast readout

- Preliminary design & schedule

## **CEPC Vertex Detector Design**

### **Detector Requirements**

- Efficient tagging of heavy quarks (b/c) and  $\tau$  leptons

- → impact parameter resolution

$$\sigma_{r\phi} = 5 \oplus \frac{10}{p(GeV)\sin^{3/2}\theta} (\mu m)$$

Detector system requirements:

- pixel occupancy: ≤ 1 %

~ µs level readout

**Target:** fine pitch, low power, fast pixel sensor + light structure

Nov.7th, 2017

Status of CEPC vertex detector R&D in China

4

Ref: Status of vertex detector, Q. Ouyang, International workshop on CEPC, Nov. 7<sup>th</sup> 2017

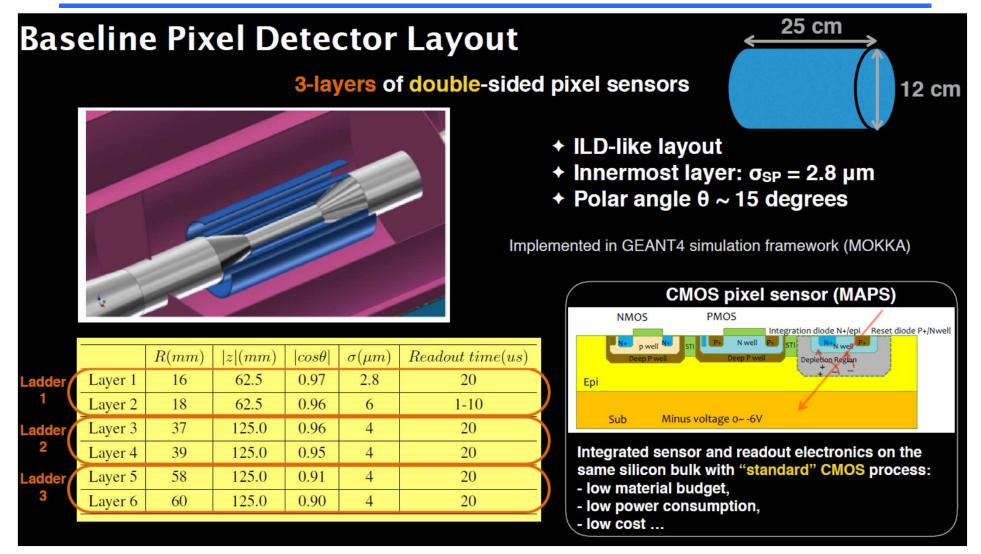

## **Baseline Vertex Detector design**

• Ref: Introduction to the Pixel MOST2 Project, Joao Costa, 2018.6

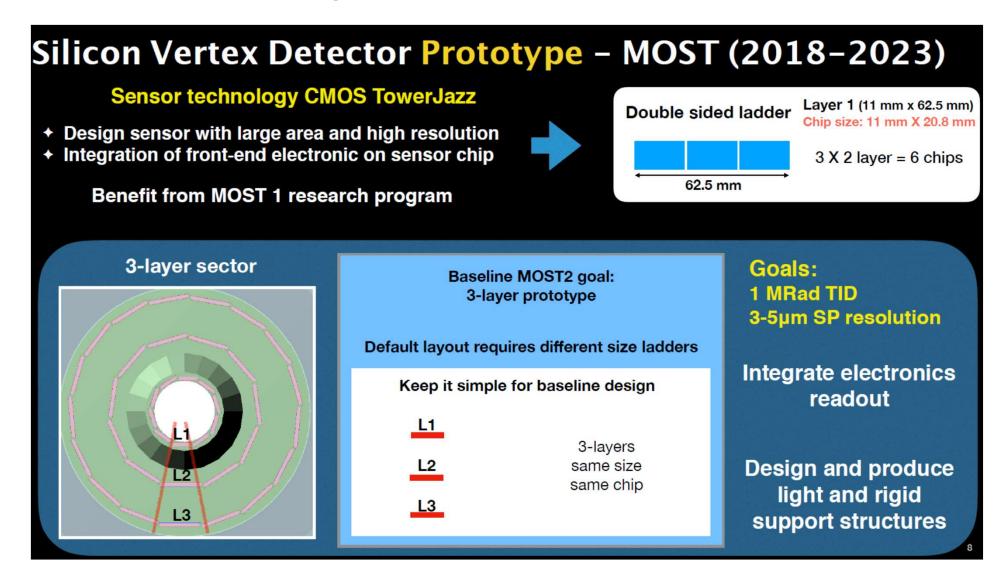

# **Ladder Prototype**

• Ref: Introduction to the Pixel MOST2 Project, Joao Costa, 2018.6

## **Previous CMOS pixel sensor prototypes**

| Prototype | Pixel pitch<br>(μm²) | Collection diode bias (V) | In-pixel circuit       | Matrix size           | R/O<br>architecture | Status            |

|-----------|----------------------|---------------------------|------------------------|-----------------------|---------------------|-------------------|

| JadePix1  | 33 × 33<br>16 × 16   | < 1.8                     | SF/amplifer            | 96 × 160<br>192 × 128 | Rolling shutter     | In<br>measurement |

| JadePix2  | 22 × 22              | < 10 V                    | amp.,<br>discriminator | 128 × 64              | Rolling shutter     | In<br>measurement |

| MIC4      | 25 × 25              | reverse bias              | amp.,<br>discriminator | 112 × 96              | Asynchronous        | In<br>measurement |

JadePix1 (IHEP)  $3.9 \times 7.9 \text{ mm}^2$

JadePix2 (IHEP)  $3 \times 3.3 \text{ mm}^2$

MIC4 (CCNU & IHEP)  $3.2 \times 3.7 \text{ mm}^2$

All prototypes in TowerJazz 180 nm process

- Slides from Y. Zhang: "IHEP CMOS pixel sensor activities for CEPC", 2018.3

- Y.P. Lu, "Pixel design and prototype characterization in China", The 2018 International Workshop on the High Energy Circular Electron Positron Collider

#### Main specs of the full size chip for high rate vertex detector

- Bunch spacing

- Higgs: 680ns; W: 210ns; **Z: 25ns**

- Meaning 40M/s bunches (same as the ATLAS Vertex)

- Hit density

- 2.5hits/bunch/cm² for Higgs/W;

0.2hits/bunch/cm² for Z

- Cluster size: 3pixels/hit

- Epi- layer thickness: ~18μm

- Pixel size:  $25\mu m \times 25\mu m$

| For                 | Specs  | For High rate | Specs                               | For Ladder<br>Prototype | Specs                                 |

|---------------------|--------|---------------|-------------------------------------|-------------------------|---------------------------------------|

| Vertex  Divel mitch | <0F.um | Vertex        | 120MH=/obje                         | J .                     | 510mm × 1004mm                        |

| Pixel pitch         | <25µm  | Hit rate      | 120MHz/chip                         | Pixel array             | 512row×1024col                        |

| TID                 | >1Mrad | Date rate     | 3.84Gbpstriggerless ~110Mbpstrigger | Power<br>Density        | < 200mW/cm <sup>2</sup> (air cooling) |

|                     |        | Dead time     | <500ns<br>for 98%<br>efficiency     | Chip size               | ~1.4cm×2.56cm                         |

# **Limitation of the existing CMOS sensors**

- None of the existing CMOS sensors can fully satisfy the requirement of high-rate CEPC Vertex Detector

- Two major constraints for the CMOS sensor

- Pixel size: should be < 25um\* 25um, aiming for 16um\*16um</li>

- Readout speed: bunch crossing @ 40MHz

- TID is also a constraint, but 1Mrad is not so difficult

|                  | ALPIDE   | ATLAS-MAPS<br>(MONOPIX /<br>MALTA) | MIMOSA | JadePix/<br>MIC4<br>(MOST1) |

|------------------|----------|------------------------------------|--------|-----------------------------|

| Pixel size       | <b>✓</b> | X                                  | ✓      | <b>✓</b>                    |

| Readout<br>Speed | X        | •                                  | X      | X                           |

| TID              | X (?)    | •                                  | •      | To be tested                |

# **New proposed architecture for MOST2**

- Similar to the ATLAS ITK readout architecture: "column-drain" readout

- Priority based data driven readout

- Modification: time stamp is added at EOC whenever a new fast-or busy signal is received

- Dead time: 2 clk for each pixel (50ns @40MHz clk), negligible compared to the average hit rate

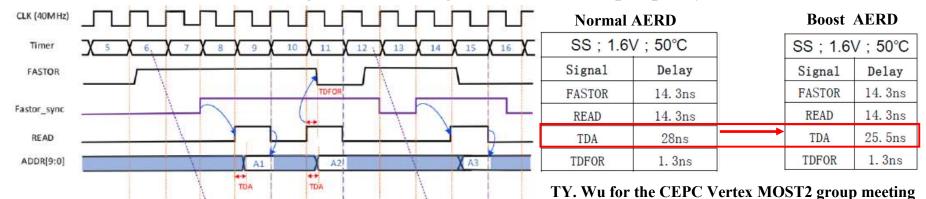

#### 2-level FIFO architecture

- L1 FIFO: In column level, to de-randomize the injecting charge

- L2 FIFO: Chip level, to match the in/out data rate between the core and interface

#### • Trigger readout

- Make the data rate in a reasonable range

- Data coincidence by time stamp, only the matched event will be readout

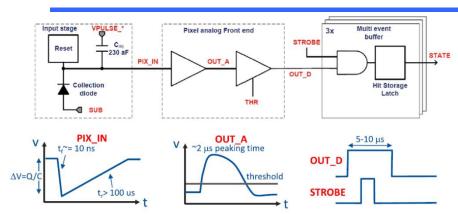

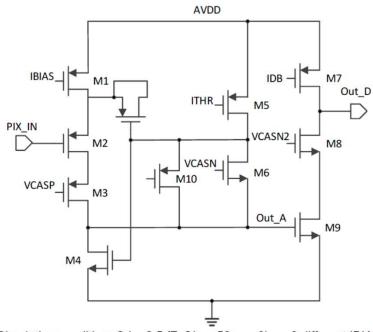

## Pixel architecture – Analog

- Digital-in-Pixel scheme: in pixel discrimination & register

- Pixel analog is derived from ALPIDE (and benefit from MIC4 for MOST1)

- As most of ATLAS-MAPS sensors' scheme

- Biasing current has to be increased, for a peaking time of ~25ns

- Now in MOST1 ~2us peaking time was designed, too slow for 40MHz BX

- Consequence:

- Power dissipation increased

- Modified TJ process for ATLAS has to be used

- ➤ With faster charge collection time, otherwise only fast electronics is of no meaning

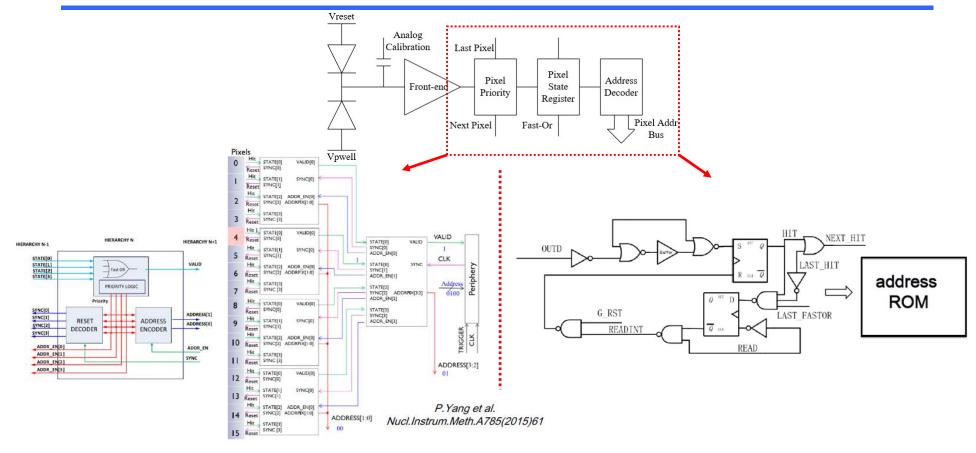

# Pixel architecture – parallel digital schemes

- Two parallel digital readout architectures were designed:

- Scheme 1: ALPIDE-like: benefit from the proved digital readout in small pixel size

- Scheme 2: FE-I3-like: benefit from the proved fast readout @40MHz BX (ATLAS)

# Design effort aiming for 40MHz BX on digital

#### ALPIDE-like scheme:

- Fast-Or bus added to record the column hit time stamp

- Boosting speed of the AERD (Address-Encoder & Reset-Decoder)

- > To shift the Fast-Or by a half of the clock cycle

- More margin in the timing constraint of the periphery circuit

#### • FE-I3-like scheme:

- Simplify the pixel cell logic

- All the logic gates were re-designed with fully customized layout

- > For smaller pixel size

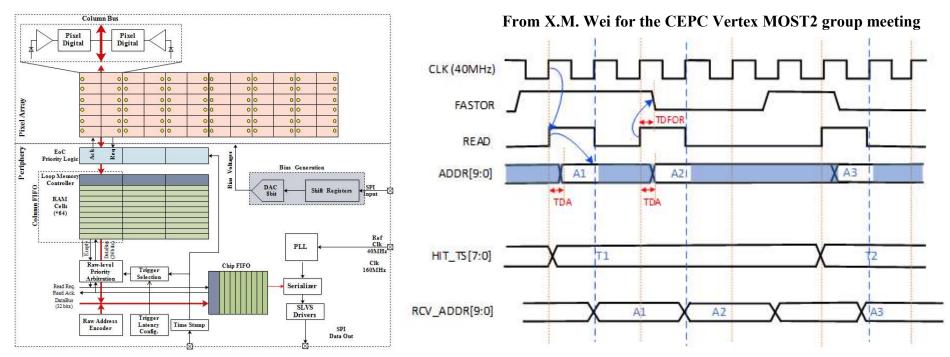

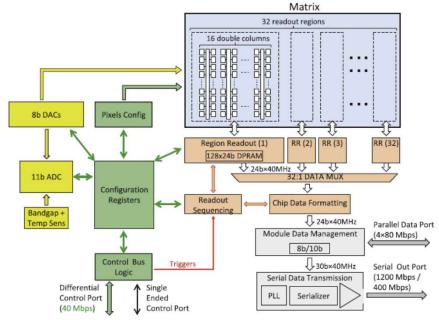

# Full chip periphery logic design

- Main Functionality:

- Trigger/Triggerless readout mode compatible

- ➤ Data coincidence and trigger window logic

- Two level FIFOs for hit derandomization

- High speed serialization for data readout

- > 4Gbps data rate capability

From X.M. Wei for the CEPC Vertex MOST2 group meeting

- Other necessary blocks

- Slow control of the pixel array and full chip via SPI interface

- Bias generation by current- and voltage- DACs

- Clock management: Phase Lock Loop and serializer

- Power management: LDOs for on-chip low ripple power supply

- High speed interface: CML & LVDS Drivers

## **Team organization**

Slides from Y. Zhang, Satellite meeting of MOST2 in Oxford, 2019.4

#### Design team:

- IHEP, SDU, NWPU, IFAE & CCNU

- Biweekly/weekly video design meeting on chip design (convened by IHEP)

| Institutes | Tasks                                                                                                | Designers                                                  |

|------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| IHEP       | Full chip modeling & simulation Pixel Analog, TCAD simulation High speed interface: PLL + Serializer | Wei Wei, Ying Zhang<br>Xiaoting Li, Weiguo Lu,<br>Mei Zhao |

| CCNU/IFAE  | Pixel Digital                                                                                        | Tianya Wu, Raimon<br>Casanova                              |

| NWPU       | Periphery Logic, LDO                                                                                 | Xiaomin Wei, Jia Wang                                      |

| SDU        | Bias generation                                                                                      | Liang Zhang                                                |

#### Chip characterization

- Test system development: SDU & + other interested parties

- Electrical test: all designers supposed to be involved in the related module + other interested parties

- Irradiation test: X-ray irradiator + beam line

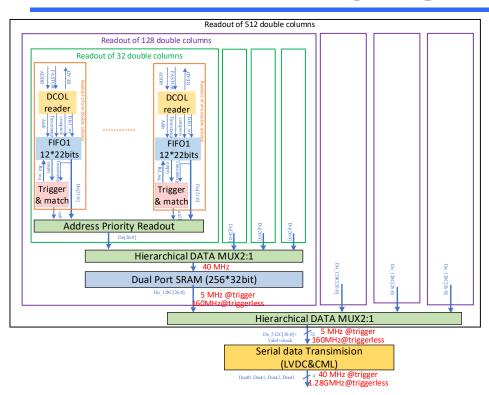

### **Current Status and recent schedule**

To be submitted in May

Expected to receive in Sep.

Test Board design will be in

parallel

#### Design Status

- Schematics of the main blocks are ready

- Layout in progress

- ➤ The first version of the pixel cell layout will be ready before the Mid of April

#### First MPW tapeout

- Shuttle booked for May 13<sup>th</sup> via IFAE

- > One block for 5mm × 5mm

- Organized with a full functional pixel array (small scale), plus other test blocks (less critical)

- ➤ A 64×192 Pixel array + Periphery + PLL + Serializer

- ➤ Bias generation included

- > I/O arranged in one edge, as the final chip

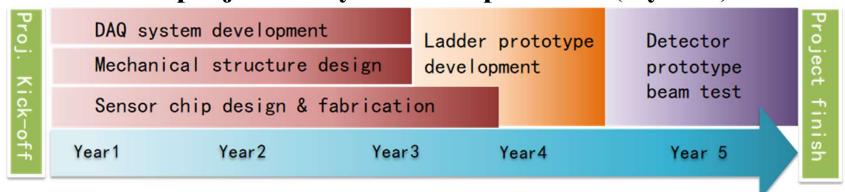

MOST2 project: May 2018 ~ April 2023 (5 years)

- Chip design plan (3 MPW & 1 engineering run in 3 years)

- Year 1: complete the preliminary design of the main functional modules of the sensor chip, submit the 1<sup>st</sup> MPW prototype, complete the design of all the functional modules

- Year 2: test the first prototype, integrate all the modules in a fully functionality chip, submit the 2<sup>nd</sup> MPW prototype, complete the 2nd prototype test

- Year 3: solve the detected bugs and finish circuit modification & improvement, fabricate and test the 3<sup>rd</sup> MPW prototype, complete the full size chip design and tapeout (engineering run)

- Slides from Y. Zhang, Satellite meeting of MOST2 in Oxford, 2019.4

# **Summary**

- Challenge considering the real CEPC's requirement

- Pixel size

- High rate & power dissipation

- None existing chip can fully satisfy the CEPC Vertex

- New proposed architecture

- Modified column-drain readout with time stamp for each hit

- Parallel verification with modified ALPIDE readout

- Trigger/Triggerless mode compatible

- Chip design for MOST2 Vertex detector is progressing almost as scheduled

- First chip submission will be delivered very soon

# Thank you!

#### The ALPIDE readout architecture

Fig. 2. Block diagram of the ALPIDE pixel cell.

Fig. 3. Block diagram of the ALPIDE chip.

G. Aglieri Rinella et al. NIM. A 845 (2017) 583-587

#### Table 1

General requirements for the pixel sensor chip for the Upgrade of the ALICE Inner Tracking System. In parentheses: ALPIDE performance figure where above requirements.

| Parameter                                                                      | Inner barrel                             | Outer barrel       |

|--------------------------------------------------------------------------------|------------------------------------------|--------------------|

| Chip dimensions (mm×mm)                                                        | 15 × 30                                  |                    |

| Silicon thickness (µm)                                                         | 50                                       | 100                |

| Spatial resolution (µm)                                                        | 5                                        | 10(5)              |

| Detection efficiency                                                           | >99%                                     |                    |

| Fake hit probability (evt <sup>-1</sup> pixel <sup>-1</sup> )                  | <10 <sup>-5</sup> (<< 10 <sup>-5</sup> ) |                    |

| Integration time (µs)                                                          | <30(10)                                  |                    |

| Power density (mW/cm <sup>2</sup> )                                            | <300(~35)                                | <100(~20)          |

| TID radiation hardness <sup>a</sup> (krad)                                     | 2700                                     | 100                |

| NIEL radiation hardness <sup>a</sup> (1 MeV n <sub>eq</sub> /cm <sup>2</sup> ) | $1.7 \times 10^{13}$                     | $1 \times 10^{12}$ |

| Readout rate, Pb-Pb interactions (kHz)                                         | 100                                      |                    |

$<sup>^{\</sup>rm a}$  10  $\times$  the radiation load integrated over the approved program (6 years of operation).

- The ALPIDE architecture, as MOST1 referenced, uses strobe signal as the "trigger"

- However, the readout rate is only ~100kHz, and more like frame readout

### Discussion on ALPIDE – analysis & conclusion

- ALPIDE is not fully compatible with CEPC vertex & other high hit rate, high bunch crossing applications (like ATLAS)

- 1. Bunch crossing too high

- Now bunch crossing at 100~200kHz (i.g. frame rate)

- While CEPC 1.5MHz (Higgs) ~ 40MHz(Z pole)

- > Not possible for the chip level frame-like readout, because:

- At least 120MHz clk has to run at periphery-column level (3pixel per hit)

- ALPIDE is "triggerless", no further data reduction, data rate too high (\*32bits per hit)

- 2. Pixel analog should be (much) faster

- now 2us peaking, 10us duration

- CEPC: "Hit rate: 120MHz/chip, or 225Hz/pixel (average), 120kHz/col (ave)",

Meaning every 8.3us, the column will be hit, however, very unlikely to be at the same pixel

- For CEPC, peaking time should be much faster (25ns level)

- > Otherwise leads to too large delay for the arrival time stamp (although can be covered by the configurable trigger match error)

- For CEPC, duration should also be faster

- > Better ends earlier than 8.3us, avoiding continuous hit in the same pixel

- Larger power expected than ALPIDE

# From vertex detector MOST1 projects towards MOST2

- To build a prototype ladder mounted with silicon pixel sensors

- Spatial resolution 3-5 μm

- TID 1 Mrad

- Compared with MOST1 project target:

- Pixel sensor prototype design

- Spatial resolution 3-5 μm

- Power consumption <100 mW/cm2</p>

- Integration time 100 μs

- MOST1 focused on key performance, however we should focus more on a full function chip that can work in a prototype system

- Baseline design for MOST2:

- Reuse the pixel design from MOST1, with necessary modification

- Focus on full chip readout architecture design, esp. fast readout and full data readout chain

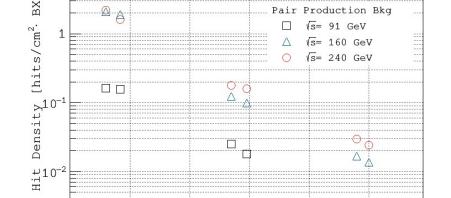

# The full size chip for high rate vertex detector

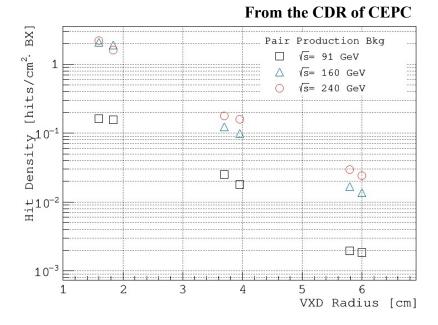

From the CDR of CEPC

VXD Radius [cm]

- Bunch spacing

- Higgs: 680ns; W: 210ns; **Z: 25ns**

- Meaning 40M/s bunches (same as the ATLAS Vertex)

- Hit density

- 2.5hits/bunch/cm² for Higgs/W;

0.2hits/bunch/cm² for Z

- Cluster size: 3pixels/hit

- The hit rate: Higgs 11 MHz/cm<sup>2</sup>, W 36MHz/cm<sup>2</sup>, Z 24 MHz/cm<sup>2</sup>

- The chip should be capable with 36MHz/cm<sup>2</sup> hit rate

- Suppose the pixel array size is 512rows\*1024cols (ALPIDE), 25um\*25um pixel size, and 1.28cm\*2.56cm pixel array area

- $\rightarrow$  Hit rate: 120MHz/chip, or 225Hz/pixel (average), 120kHz/col (ave)

- Meaning every 8.3us, the column will be hit, however, very unlikely to be at the same pixel

- In order to readout without data loss, time stamp has to be added for every hit

- According to the readout speed of MOST1(10~100us), it is not capable for this large hit rate

- Also MOST1 chip design (MIC4) is currently base on ALPIDE readout architecture, which is still more or less frame-based, not fully capable with trigger readout

#### Increased data rate as for the real CEPC

- Every hit has 27~32bits (async): col addr 9bits (512), row addr 10bits (1024), time stamp ~8bits (suppose 40MHz clock, covers 6.4us time region)

- If triggerless, all the raw hit data should be sent off chip

- The data rate: ~32bits\*120MHz= 3.84Gbps, possible, but risk too high in the current stage

- If trigger, on-chip buffer should be designed

- Suppose trigger latency 3us. Trigger rate was said 20kHz~50kHz

- Triggered data rate:

- > 2.5/hits/bunch/cm<sup>2</sup>\*3pixels/hit\*1.28cm\*2.56cm\*32bit=786bit/bunch/chip

- ➤ W@20kHz trigger rate -> 15.7Mbps/chip as the triggered data rate

- In order to cover any trigger error(mismatch of the edge in different column, time walk of the hit peaking...)

- $\triangleright$  A trigger window can be set, so that the data within the  $\pm \sigma$  of the trigger time stamp can all be read out

- ➤ In this way, the readout data rate will be (suppose trigger window of ±3LSB time stamp):

- 15.7Mbps \* 7 ~ 110Mbps

- Can still be read out by a single LVDS interface

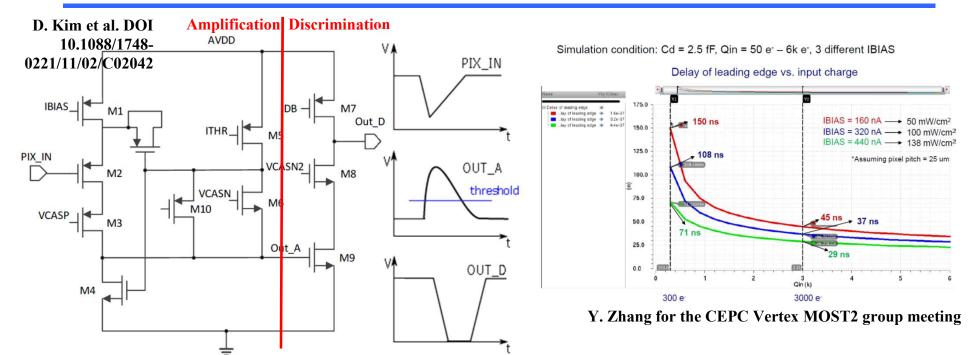

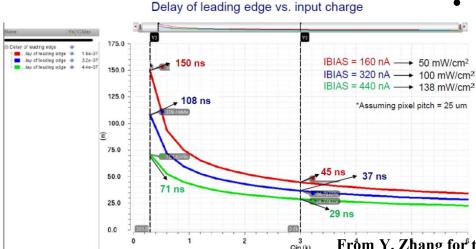

# Other necessary modification for the pixel cell

Simulation condition: Cd = 2.5 fF, Qin = 50 e- 6k e-, 3 different IBIAS

3000 e

300 e

- Pixel analog in the same architecture as ALPIDE (and benefit from MIC4 for MOST1) but with different parameters

- Aiming especially for fast readout

- Biasing current has to be increased, in order to achieve a peaking time of ~25ns

- Otherwise there will be timing error for the event, and has to open a trigger window in this case

- Now in MOST1 ~2us peaking time was designed, which is too slow for 40MHz BX

#### **Consequence:**

- Power dissipation increased:

- bias@440nA with peaking time 29ns, but 138mW/cm² for analog

- > Total power density may exceed 200mW/cm<sup>2</sup>

- Modified TJ process for ATLAS has to be used

- > With faster charge collection time, otherwise only fast electronics is of no meaning

From Y. Zhang for the group meeting