## LHCb VELO Readout

Karol Hennessy on behalf of LHCb November 18, 2019

University of Liverpool

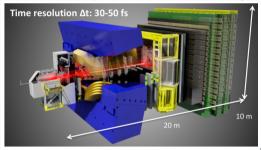

#### LHCb

Covering about 4% of the solid angle in the forward region, the detector captures 40% of the beauty cross-section

- Beam crossing rate 40 MHz

- $10^5$  beauty pairs per second

- Selection of interesting events is mandatory

LHCb VELO Readout — November 18, 2019 — K. Hennessy

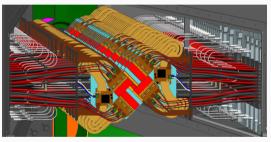

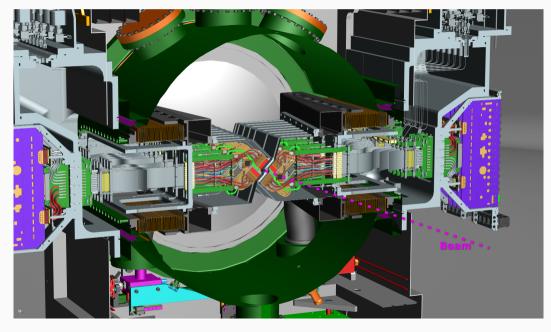

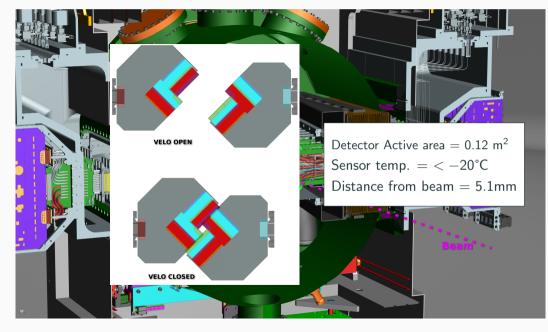

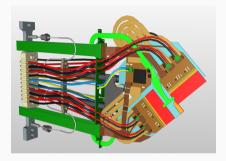

- Vertex Locator (VELO) for the upgraded LHCb detector

- Silicon pixel modules around the LHC beam interaction region

- 50fb<sup>-1</sup> integrated luminosity for LHC Runs 3 & 4

- Very high radiation environment

- maximum fluence approx.  $8{\times}10^{15}$   ${\rm MeV}\cdot n_{\rm eq}/{\rm cm}^2$

- In vacuum and under active cooling

• LHCb has triggerless readout - full detector readout @ 40 MHz

LHCb Vertex Locator

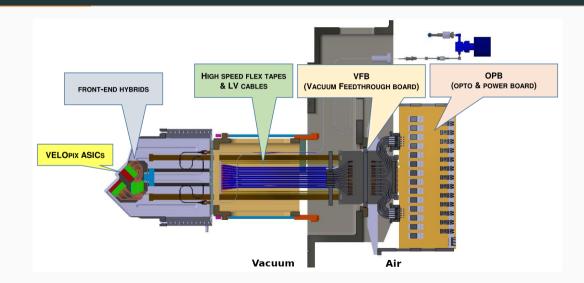

**VELO CAD**

#### **VELO Electronics**

LHCb VELO Readout — November 18, 2019 — K. Hennessy

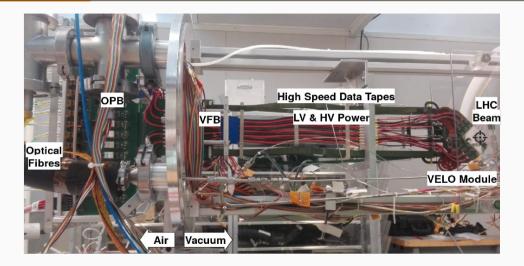

#### **VELO Electronics Lab**

#### **VELO** in Numbers

| Feature                 |                                         |

|-------------------------|-----------------------------------------|

| Sensors                 | Pixels                                  |

| # of modules            | 52                                      |

| Detector Active area    | $0.12 m^2$                              |

|                         | ${\sim}41$ M pixels                     |

| Technology              | electron collecting                     |

|                         | 200 $ m \mu m$ thick                    |

| Max fluence             | $8	imes 10^{15}~{ m MeVn_{eq}/cm^{-2}}$ |

| HV tolerance            | 1000 V                                  |

| ASIC Readout rate       | 40 MHz                                  |

| Total data rate         | 2+ Tb/s                                 |

| Total Power consumption | 2.2-2.3 kW                              |

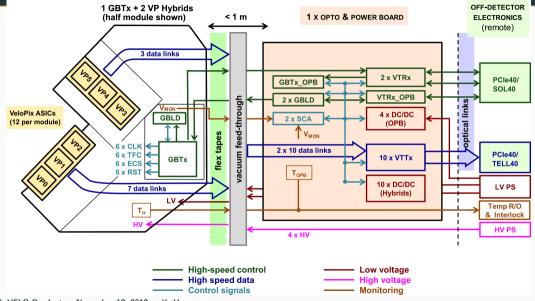

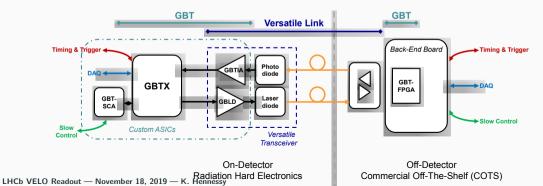

#### **High Speed Pathways**

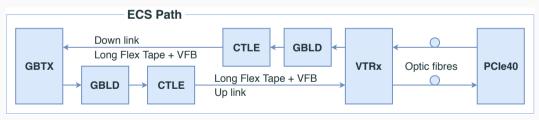

ECS - Experiment Control System

- Bi-directional with **GBTx** ASIC

- 4.8 Gb/s

- Use of GBLD as electrical line driver (emphasis and amplification functionality)

CTLE - Continuous Time Linear Equaliser

#### **GBT** - **ECS** interface

- The **GBTX** chip is a radiation tolerant chip for LHC experiments

- GBT Protocol can utilise three logical data paths

- Trigger and Timing Control (TTC)

- Slow Control (SC) via companion SCA chip

- Data Acquisition (DAQ) (NOT used for VELO)

- All three logical paths can be encapsulated on a single physical interface

11/28

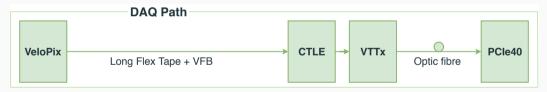

#### DAQ - Data Acquisition

- Uni-directional (from VeloPix to back-end)

- 5.12 Gb/s

- VeloPix has some internal emphasis

Similar electrical transmission lines for ECS and DAQ - expect similar performance.

- Front-end ASIC driving the design of the VELO data acquisition system

- Operates at LHC clock rate  $\sim 40 \text{MHz}$

- Designed for high radiation tolerance and low power consumption

- Custom output serialiser Gigabit Wireline Transmitter (GWT)

- Slow control via SLVS protocol

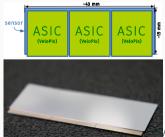

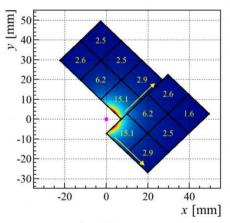

- 12 VeloPix chips per module

- 20 readout links (more links for hotter chips)

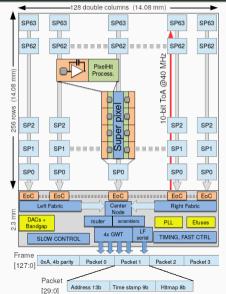

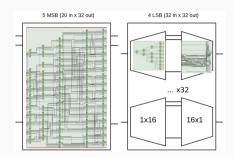

### VeloPix ASIC

- Readout is data driven only read out when they have "hits above threshold" (a.k.a. zero-suppression)

- Binary readout @ 40 MHz

- VeloPix is optimised for high speed readout

| Peak hit rate | 900 Mhits/s/ASIC |

|---------------|------------------|

| Max data rate | 19.2 Gb/s        |

| Total VELO    | 2.85 Tb/s        |

- Power consumption  $< 1.5 \ {\rm W}{\cdot}{\it cm}^{-2}$

- Radiation hard 400 Mrad, and SEU tolerant

- Non-uniform radiation dose

LHCb VELO Readout — November 18, 2019 — K. Hennessy

Average data rate

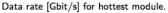

#### Hybrids

- VeloPix Hybrids

- 20 high-speed data links @ 5 Gb/s

- 4 hybrids per module (2 per side)

- GBTx Hybrid

- Timing and control signals

- GBLD as a line driver

GBT - http://cern.ch/go/6rsK

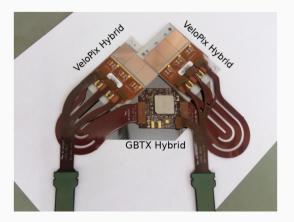

#### Hybrid, Cables, Feedthough

- High speed flex tapes

- Stripline tech. 200 μmtrack & gap, 175 μmPyralux

- length 550, 561, 575 mm

- Vacuum Feedthrough board

- bringing all LV, HV, data, control signals to/from modules in vacuum

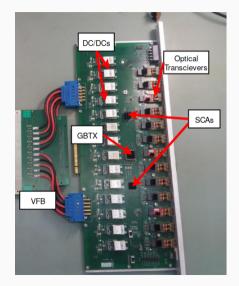

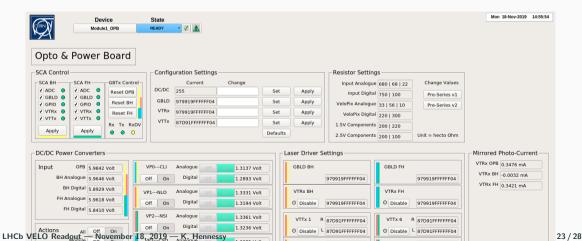

#### **Opto-Power Board**

- Situated on VELO tank exterior

- Connects to Vacuum Feedthrough Board

- Fibres to counting room at surface ( $\sim$  300 m)

- Interface for data, control, monitoring signals and powering for VELO modules

- FeastMP DC/DCs for power

- Voltage monitoring

- Optical transceivers (VTTx/VTRx) for driving to/from backend

- Control via GBTx and SCA

$\mathsf{GBT}\text{-}\mathsf{SCA}\text{ - }\mathsf{http://cern.ch/go/Zcc9}$

#### VeloPix Data readout

- Pixel data is aggregated into groups of 2×4 called **SuperPixels**

- 30% reduction in data size

- Data is sent out-of-time ⇒ timestamp stored in SuperPixel data packet

- Custom serializer Gigabit Wireline Transmitter (GWT)

- Low power 60 mW

- 5.12 Gb/s line rate

- GWT protocol

- scrambled data

- parity check, no error recovery

- $\bullet \ \Rightarrow \ \text{minimise bit error rate}$

LHCb VELO Readout — November 18, 2019 — K. Hennessy

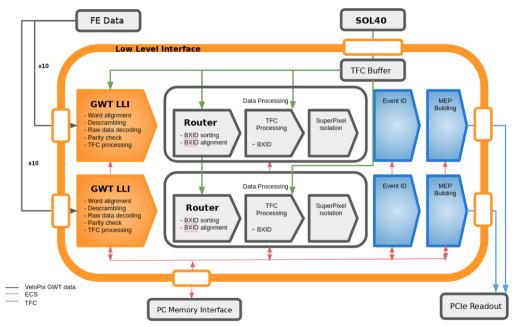

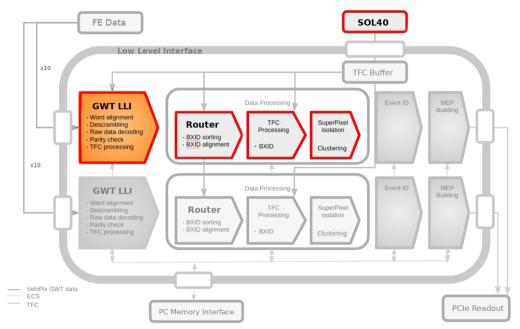

#### Backend DAQ and Slow Control - PCIe40

- Single control and readout board for the entire experiment

- Can be used for TFC, SC, or DAQ or all

- Common hardware, shared firmware components

- PCle Gen3 x16

- Intel Arria10 FPGA (10AX115S4F45E3SG)

- High power consumption up to 80W FPGA, ~57W card

- up to 4 PCIe40 per chassis (ASUS ESC4000-G3, 2x Xeon 3 GHz, 8x 8 GB DDR4)

LHCb VELO Readout — November 18, 2019 — K. Hennessy

PCIe40 - http://cern.ch/go/HQ6P

- 48 bi-directional links (or 96 uni-directional) @ ~5 Gb/s

- Output bandwidth 100 Gb/s (measured).

### LHCb/VELO Firmware

- Common PCIe hardware allows for software-like firmware design

- Custom components in a global framework

- Common build and simulation environment

- Gitlab allows for continous integration/deployment

- Automated Versioning and tracability

- Automated testing

- Issue tracking

- User extensible

- Same hardware deployed to labs/institutes with timing, control and DAQ in one box

LHCb VELO Readout - November 18, 2019 - K. Hennessy

LHCb VELO Readout - November 18, 2019 - K. Hennessy

#### **Control Software**

- Software for configuring the electronics and readout

- Siemens WinCC-OA & Joint COntrols Project @ CERN (JCOP)

#### **Quality Assurance**

- IV curves, power consumption monitoring, voltage drops

- Band Gap Calibration best estimate of sensor temperature

- VeloPix equalisation and Noise scan

- Testpulse data taking over high speed links

- Bandwidth saturation tests of HS links

- All full module tests compared to individual component tests

Https://www.overleaf.com/8979545789zcsvndjkyyjd

#### 1 Setup of Opto-& Power Board

a: The latest stable firmware to use is lhcb\_daq\_firmware\_v61\_20190406\_1\_stp.working.sof and has 6 GBT and 20 GWT links. Connect the optical fibres to the VTTx sockets according to the following mapping: (see Fig. 1)

Velo Module: Electrical Testing Checklist

Kristof De Bruyn August 13, 2019

| Link                    | 0        | 1             | 2              | 3       | 4        | 5        | 6        | 7       | 8        | 9        | 10      | 11      |

|-------------------------|----------|---------------|----------------|---------|----------|----------|----------|---------|----------|----------|---------|---------|

| MPO 0: Fibre ID<br>Slot | 6<br>OPB | $^2_{\rm BH}$ | 4<br>FH        | 8       | 10       | 12       | 11<br>1R | 9<br>1L | 7<br>2R  | 5<br>2L  | 3<br>3R | 1<br>3L |

| MPO 2: Fibre ID<br>Slot | 2<br>4R  | 4<br>4L       | $\frac{6}{5R}$ | 8<br>5L | 10       | 12       | 11       | 7       | 9        | 5        | 3       | 1       |

| MPO 3: Fibre ID<br>Slot | 2<br>6R  | 4<br>6L       | 6<br>7R        | 8<br>7L | 10<br>8R | 12<br>8L | 11<br>9R | 9<br>9L | 7<br>10R | 5<br>10L | 3       | 1       |

- $\hfill\square$  b: Launch the MiniDAQ configuration panel using the alias wccmd or wccopb. (see Fig. 2)

- C: Make sure the (default) settings for the MiniPod and Subdetector Type match the fibre mapping: (see Fig. 2).

| Link        | 0   | 1    | 2    |

|-------------|-----|------|------|

| MiniPod     | Tx  | Rx   | Tx   |

| Subdetector | OPB | Velo | Velo |

- □ d: Click the buttons Set Polarity and Set Detector. The yellow squares should turn green.

- $\hfill\square$  e: Launch the OPB configuration panel using the alias wccopb. (see Fig. 3)

- □ f: Step 1: Click the two activate buttons. All five boxes in the R column should get ticked and the three LEDs showing Tx & Rx Ready should become green.

- □ g: Step 2: Click the Power On button for GBTz/GBLD, Linkl, Link2 and the tiles you wish to power; or use the All On button. The LEDs should switch from red (off) to green (on) and the displayed voltages should be non-zero.

- I: Step 3: Click the All Config button. The LEDs should switch from yellow (Not Set) to green (OK).

#### QA of High speed links

- PRBS test for high speed readout

- Slow control communication tests with OPB and VeloPix

- Timing and fast control checks

| Vision_1                                                                                     | : VP_DEV/velo_\       | /eloPix/Communicatio | n.pnl          | _ 0 ×                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|----------------------------------------------------------------------------------------------|-----------------------|----------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VeloPix                                                                                      | VeloPix Communication |                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Front Hybrid GBTx                                                                            | Clear Reset           | Back Hybrid Gl       | BTx            | Clear Reset                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Front Hybrid                                                                                 |                       | Back Hybrid          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| VP0 - Asic 0<br>VP0 - Asic 1<br>VP0 - Asic 2<br>VP0 - Asic 2<br>VP0 - Asic 2<br>VP0 - Asic 2 |                       | VP2 - Asic 0 -       | - VP2 - Asic 1 | VP1 - Asic 2 -           reard         Vent           reard         Vent           reard         Vent           vP1 - Asic 1 -         -           reard         Vent           reard         Vent |  |  |

| LHCb VELO Readout -                                                                          | Novem                 | ber 18, 201          | 9 — K. I       | lennessy                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

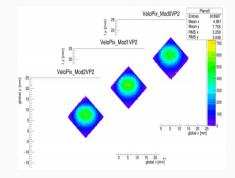

#### Testbeam Q4 2018

- Performed at CERN just prior to the Long Shutdown of SPS

- VeloPix and sensors had been tested in previous beam tests, but never with full high-speed readout, and complete LHCb slow control and DAQ chain

- Synchronised with Timepix 3 telescope. Allows to check time alignment < 1 ns</li>

#### Testbeam Q4 2018

- Successfully took high-speed data from VeloPix synchronised between 3 module planes

- HV scans, Time-over-Threshold scans, Ikrum (Krummenacher current) scans

- Synchronisation tests

- Integrated with LHCb PCle40 firmware and software

- Several other testbeam and irradiation campaigns to qualify VELO sensors

#### Conclusion

- Vertex Locator with high-speed readout in vacuum

- Leveraging many rad-hard components developed at CERN and within the collaboration

- VeloPix culmination of many years of rad-hard ASIC development for tracking

- Common readout platform for LHCb with VELO customisations

- Good performance of high speed links with full module control and readout chain

Thank You

# Backup

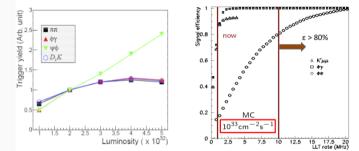

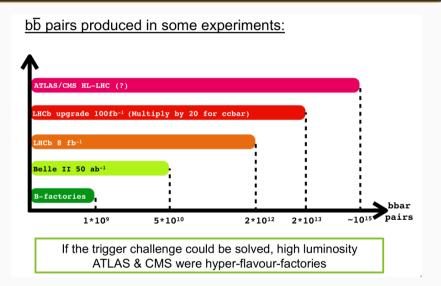

#### The need for an upgrade

Due to the available bandwidth and the limited discrimination power of the L0 trigger, LHCb experiences the **saturation of the trigger yield** on hadronic channels at around  $4. \times 10^{32}$  cm<sup>-2</sup>s<sup>-1</sup>.

With the **upgraded detector it** will be possible to increase the physics yields by a factor 10 in the decays with muons, a factor 20 for hadronics channels, collecting ~  $50 fb^{-1}$  running at  $1-2 \times 10^{32}$  cm<sup>-2</sup>s<sup>-1</sup> 10 times the current design luminosity but with increased complexity

(pileup greater a factor 5).

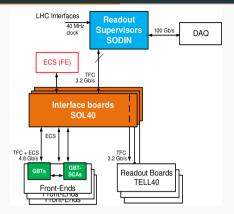

### Timing and Fast Control (TFC)

- Single Readout Supervisor provides a clock and timing commands to front-end and back-end electronics

- BXID Reset, FE Reset, BE Reset, Sync, ...

- Interfaces with LHC

- TFC commands are fixed latency

- Data are *NOT* fixed latency

- For VELO, TFC synchronisation commands form "special" GWT packets and sent immediately from front-end

- (standard data packets are sent out-of-time)

- 10G PON network with optional feedback

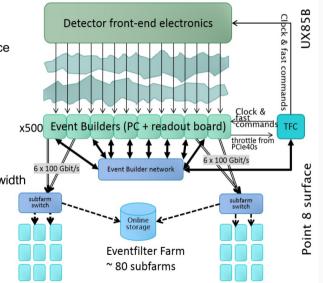

# Architecture

Distance between FE and RO : ~350m

- ~15000 optical links

- ~ ~ 500 readout boards

- ~24 links in average on each board

- ~100 kbytes per event

- ~32 Tb/s aggregate bandwidth

#### MiniDAQ - All in one solution

- MiniDAQ = PCIe40 + server

- The MiniDAQ platform allows for controls, DAQ, and software all to run in a **standalone system**

- The server is provided with the PCle40 installed, necessary programming cables and OM3 fibres

- WinCC JCOP software comes pre-installed (a licence is needed)

- All necessary drivers and support software is installed

- With one server, one can control the front-end hardware and at the same time read out its data.

#### b-b pairs produced

#### LHCb facts

- New data centre being constructed (2 MW)

- 4000 U in 6 container modules

- 400+ Gb/s to CERN IT

- Studying HPC FPGA, GPU, ML...

- Biggest/fastest readout system to date

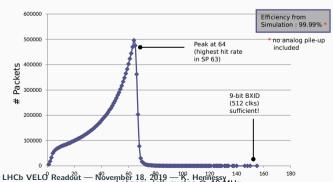

#### **BXID** Router

- Time-ordering SuperPixel data

- 9-bit router sorts data 1 bit at a time

- Extensive simulation required both to maximise speed (¿160 MHz) and minimise FPGA resource usage

- Latency limit ; 512 clock cycles

#### **ECS Software**

- Control system modelled with finite state machine tree

- commands propagate down; status propagates up

- Integrates with SOL40, TELL40, SODIN

- Can integrate with COTS hardware (CAEN, ISEG, Wiener...)

- Rapid development

- Oracle database backed

- Archiving, trending, alarm functionality...

| Device M    | lanager 🤣                     |

|-------------|-------------------------------|

|             | 💿 Operation 🛛 🔵 Configuration |

| Running on: | System1                       |

| Hardware    | Logical FSM                   |

| - (<br>- (  | stem1:<br>MiniDAQ             |

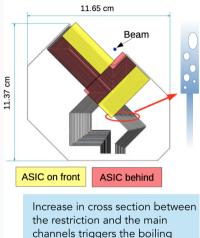

# Micro-channel cooling

C. Bertella

17-October-2019

500 µm thick silicon substrate

Input restrictions:

- 60 x 60 μm , 40 mm long

- Dominant pressure drop

- Flow Prevent instabilities among the channels

Main channels

- 120 x 200 μm

- [230, 290]mm long

- Heat is absorbed by the CO<sub>2</sub>: change in gas/liquid ratio

#### Refs

- GBT

- GBT-SCA

- PCle40