# **HV-CMOS** sensors for the outer Tracker

Marcello Borri, John Dainton, <u>Harald Fox</u>, Yanyan Gao, Roy Lemmon, Daniel Muenstermann, Ivan Peric, Rudolf Schimassek, Hongbo Zhu

> STFC Daresbury Laboratory Lancaster University The University of Edinburgh Karlsruhe Institute of Technology Institute of High Energy Physics, CAS

### Introduction and Overview

Progress and developments since the first idea was presented by Daniel Muenstermann at the Oxford CEPC workshop this year:

https://indico.cern.ch/event/783429/contributions/3379826/attachments/1831027/2998576/ Muenstermann\_CMOS-for-CEPC.pdf

In this talk:

- 1. CEPC tracker layouts and requirements from CDR

- 2. Sensors: ATLASPix3

- 3. Sensor readout: Flex & YARR

- 4. Staves: The ALICE experience

- 5. Conclusions and summary

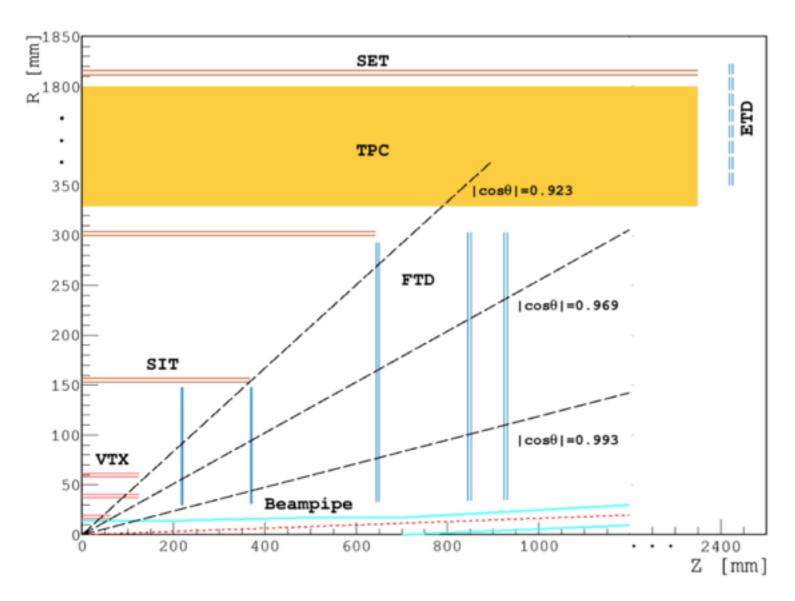

#### CEPC tracker designs: TPC/Si

Baseline tracker design: TPC

and 3 layers / 5 disks of silicon sensors,

50 m<sup>2</sup> if built in CMOS pixels (strips default)

| Detector |         | Radiu        | s <i>R</i> [mm] | ±z [mm] | Material budget $[X_0]$ |

|----------|---------|--------------|-----------------|---------|-------------------------|

| SIT      | Layer 1 | 153          |                 | 371.3   | 0.65%                   |

| 511      | Layer 2 | 300          |                 | 664.9   | 0.65%                   |

| SET      | Layer 3 | 1            | 811             | 2350    | 0.65%                   |

|          |         | $R_{\rm in}$ | $R_{out}$       |         |                         |

|          | Disk 1  | 39           | 151.9           | 220     | 0.50%                   |

|          | Disk 2  | 49.6         | 151.9           | 371.3   | 0.50%                   |

| FTD      | Disk 3  | 70.1         | 298.9           | 644.9   | 0.65%                   |

|          | Disk 4  | 79.3         | 309             | 846     | 0.65%                   |

|          | Disk 5  | 92.7         | 309             | 1057.5  | 0.65%                   |

| ETD      | Disk    | 419.3        | 1822.7          | 2420    | 0.65%                   |

| Operation mode                         | H (240) | W (160) | Z (91) |

|----------------------------------------|---------|---------|--------|

| Track multiplicity (BX <sup>-1</sup> ) | 310     | 300     | 32     |

| Bunching spacing (ns)                  | 680     | 210     | 25     |

| SIT-L1 occupancy (%)                   | 0.19    | 0.58    | 0.52   |

| FTD-D1 occupancy (%)                   | 0.17    | 0.54    | 0.48   |

Table 4.6: Estimated occupancies of the first layers of the SIT (SIT-L1) and the FTD (FTD-D1). See context for more details.

H. Fox

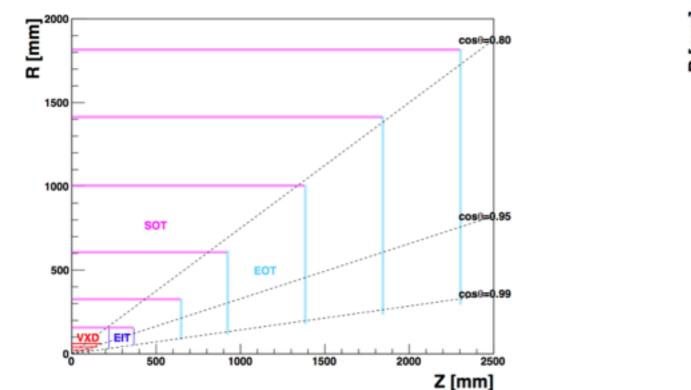

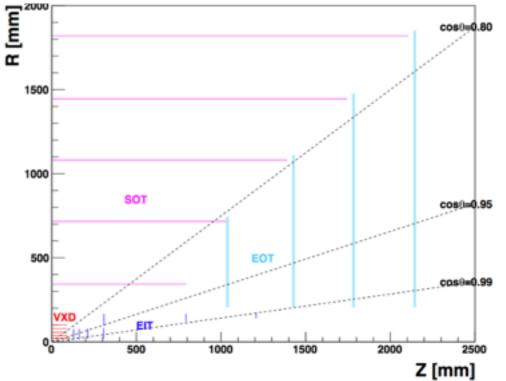

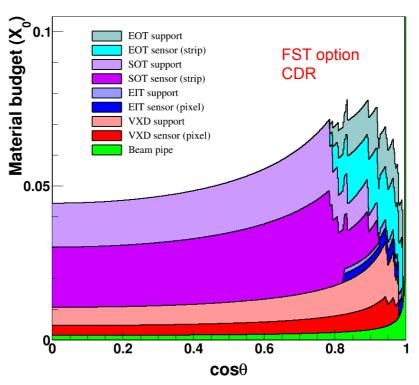

## CEPC tracker designs: FST / FST2

Full silicon alternatives: FST: 98 m<sup>2</sup> in CMOS FST2: 101 m<sup>2</sup> in CMOS Alice ITS: ~10 m<sup>2</sup>; ATLAS upgrade Pixel ~14m<sup>2</sup>

FST and FST2 configurations. The total radiation length, including dead material such as the readout, for the entire tracking system is about  $5-7\%X_0$  for the FST and  $7-10\%X_0$  for the FST2.

|         |              | FSI           |             |      | FST2         |               |             |      |  |  |

|---------|--------------|---------------|-------------|------|--------------|---------------|-------------|------|--|--|

| SOT     | R (m)        |               | $\pm z$ (m) | Туре | R (m)        |               | $\pm z$ (m) | Туре |  |  |

| Layer 1 | 0.153        |               | 0.368       | D    | 0.3          | 344           | 0.793       | s    |  |  |

| Layer 2 | 0.321        |               | 0.644       | D    | 0.1          | 718           | 1.029       | s    |  |  |

| Layer 3 | 0.603        |               | 0.920       | D    | 1.0          | 082           | 1.391       | S    |  |  |

| Layer 4 | 1.000        |               | 1.380       | D    | 1.446        |               | 1.746       | s    |  |  |

| Layer 5 | 1.410        |               | 1.840       | D    | 1.820        |               | 2.107       | s    |  |  |

| Layer 6 | 1.811        |               | 2.300       | D    |              |               |             |      |  |  |

| EOT     | $R_{in}$ (m) | $R_{out}$ (m) | $\pm z$ (m) | Туре | $R_{in}$ (m) | $R_{out}$ (m) | $\pm z$ (m) | Туре |  |  |

| Disk 1  | 0.082        | 0.321         | 0.644       | D    | 0.207        | 0.744         | 1.034       | D    |  |  |

| Disk 2  | 0.117        | 0.610         | 0.920       | D    | 0.207        | 1.111         | 1.424       | D    |  |  |

| Disk 3  | 0.176        | 1.000         | 1.380       | D    | 0.207        | 1.477         | 1.779       | D    |  |  |

| Disk 4  | 0.234        | 1.410         | 1.840       | D    | 0.207        | 1.852         | 2.140       | D    |  |  |

| Disk 5  | 0.293        | 1.811         | 2.300       | D    |              |               |             |      |  |  |

**Figure 4.23:** R - Z views of the full-silicon tracker options, FST (top) and FST2 (bottom). In the FST layout, the full strip detector (SOT and EOT) is composed of double silicon strip layers. In the FST2 layout, the SOT consists of single layers, while the EOT consists of double-strip layers.

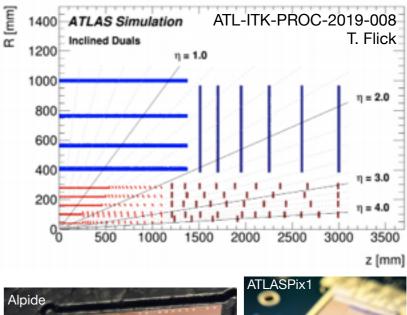

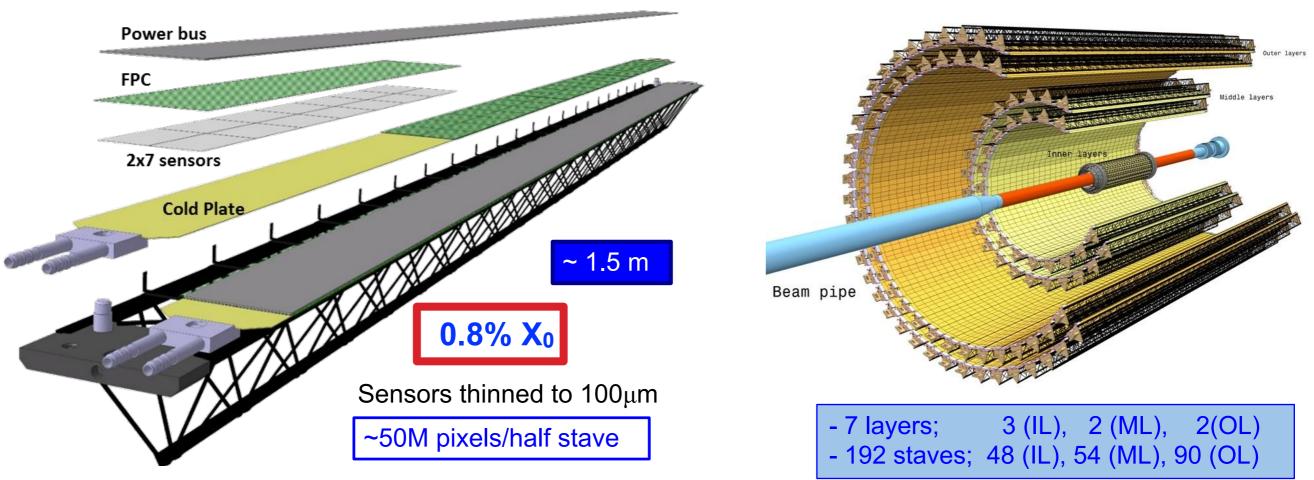

## ATLAS/ALICE concepts for the CEPC

#### **Comparison:**

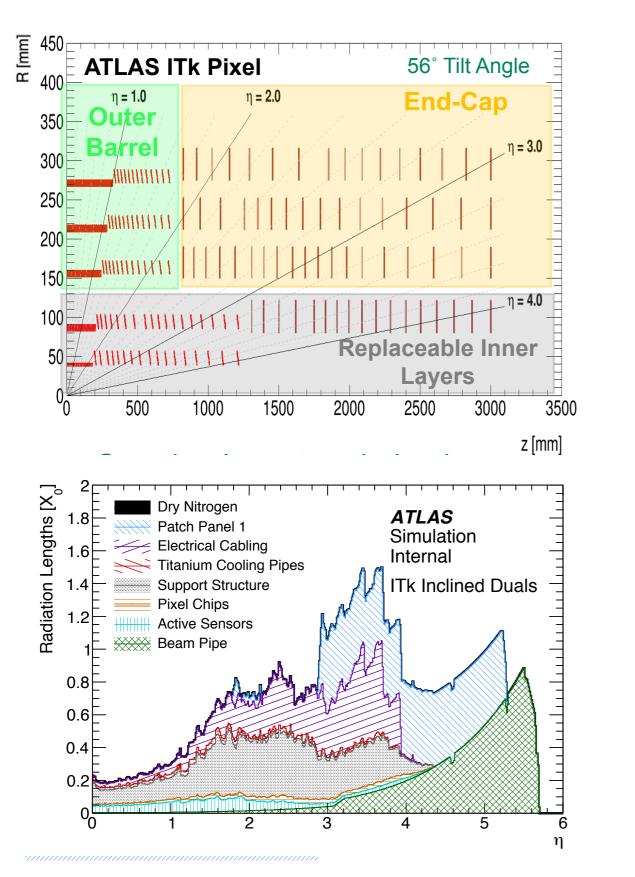

25ns bunch spacing (Z-mode): same for ATLAS O(100 m<sup>2</sup>) of silicon tracker: comparable for the ATLAS ITK pitch/resolution: 50 μm in φ ALICE ITS: 29μm x 27μm monolithic CMOS ATLAS ITK Pixel CMOS: < 50μm x 150μm

material budget for tracker layers: 0.65% (TPC/Si)/~1% (Full Si) X/X<sub>0</sub> / layer

ALICE: 0.8%/layer outer barrel staves

H. Augustin eg. al,, Uni Heidelberg

ATLAS: ITK Pixel <1X<sub>0</sub> total (standard hybrid, Ti cooling pipes, all supports & services)

https://www.unige.ch/dpnc/en/groups/giuseppe-iacobucci/research/slim-mechanics/

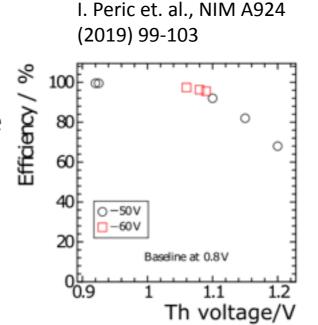

#### Sensor proposal: ATLASPix

#### ATLASPix is a CMOS sensor developed to fulfil the requirements for the ATLAS upgrade

- Not strictly an ATLAS development

- Monolithic CMOS allows to produce large areas fast and cheap

- No hybridisation wirebonds or C4NP bumps possible

- 25ns timing compliant

- Hit efficiency 99.5% (ATLASPix1)

- Pixel size 150 μm by 50 μm (or smaller)

- Triggered or triggerless readout possible

- 1.28 GBit/s downlink

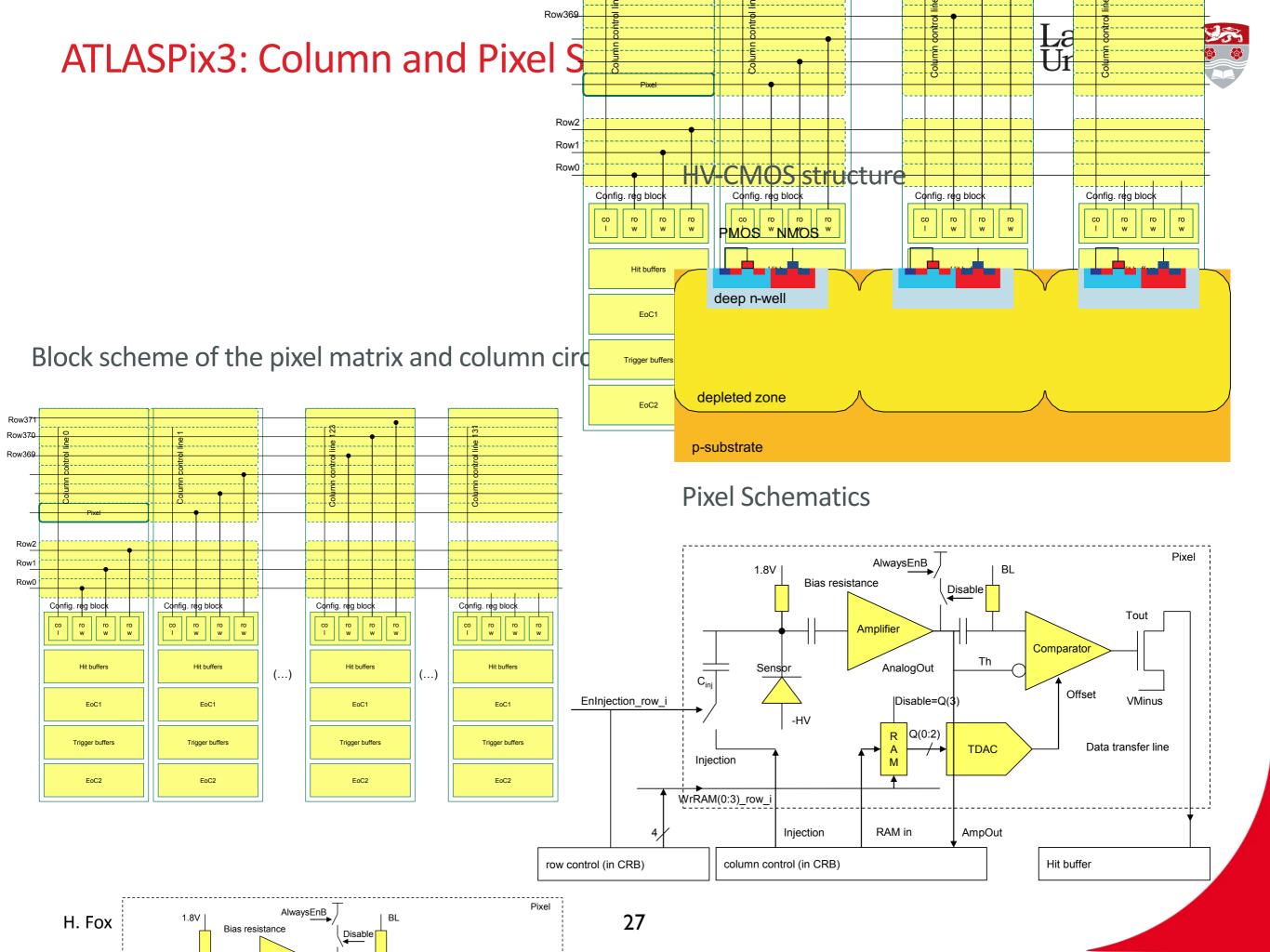

#### ATLASPix3

- Reticule size: 2.02 cm by 2.1 cm

- Full-size sensor, ATLASPix3 (TSI, 200Ωcm, 180nm) just delivered

- $\bullet$  132 columns with 150 $\mu m$  pixel

- One column contains 372 pixels, a configuration register block, 372 hit buffers, 80 trigger buffers and two **end of column (EoC) blocks**. EoC1 is attached to hit buffers and EoC2 to trigger buffers.

6

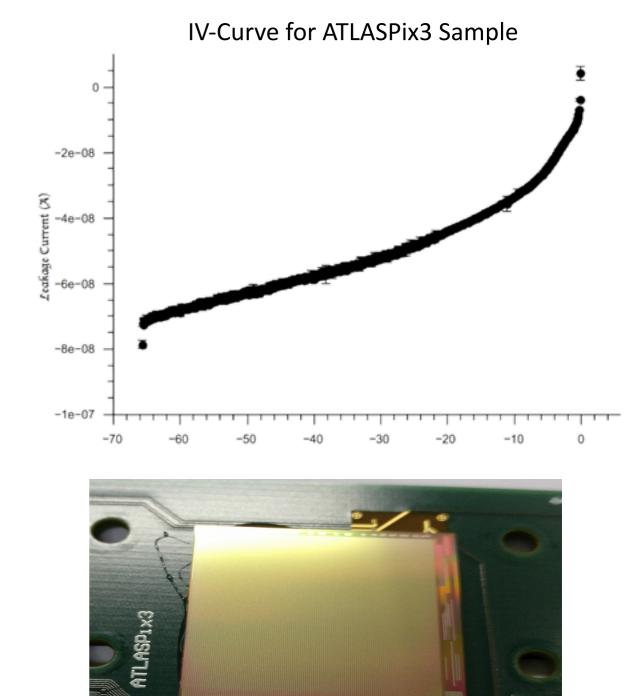

## ATLASPix3: First measurements

#### Sensor:

Chip powered during measurement. Low leakage current of < 50 nA @ -20 V Breakdown around -66 V

• There are ideas how this could be increased if necessary.

#### **Configuration and Readout:**

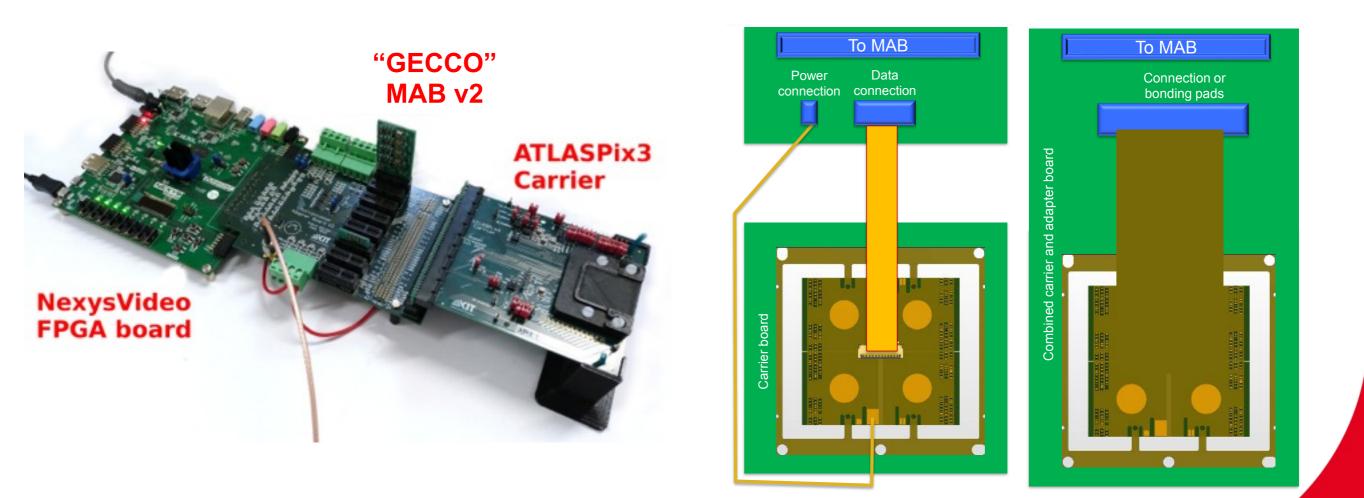

**SPI** (Serial Peripheral Interface in, out, clock, select) configuration tested to work

**RAM** writing is working

Untriggered **readout** tested to work at 400 Mbps (DDR, results in 25 ns time stamp)

**To do**: High speed link (data-clock-in, data-out) at full speed for e.g. YARR; Triggered readout; Command decoder; Clock recovery

7

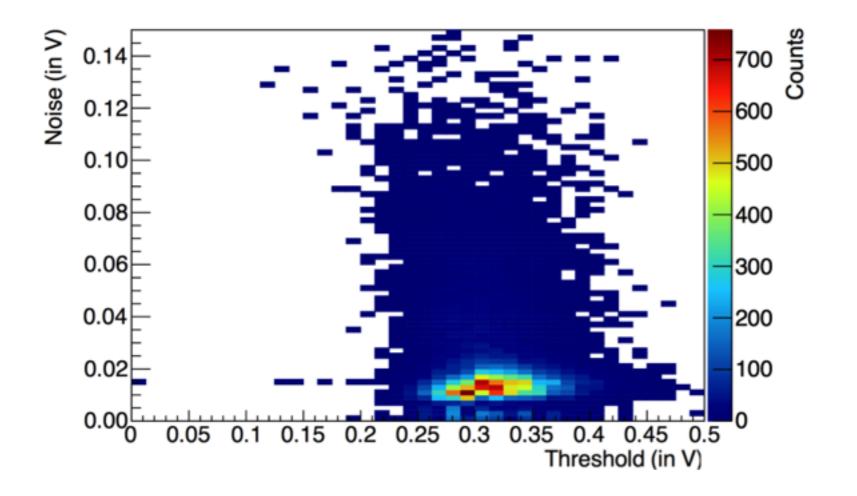

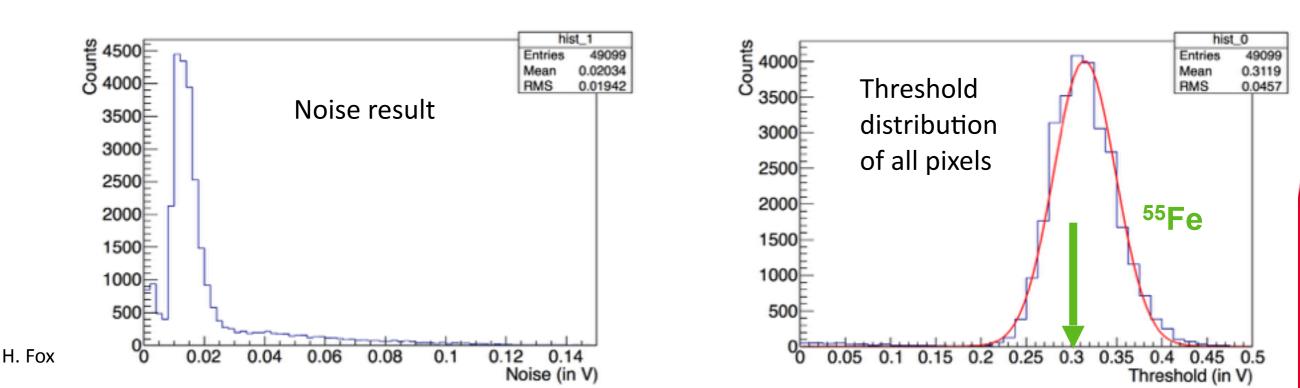

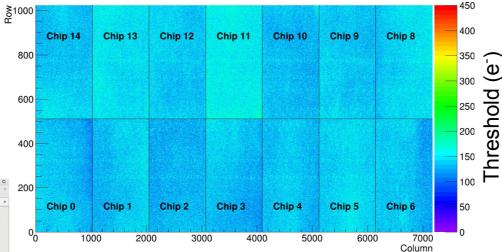

## **Threshold and Noise**

Charge of increasing strength injected into the pixels Fraction of detected signals measured Shifted and scaled step function convoluted with a Gauss is fitted to the data points

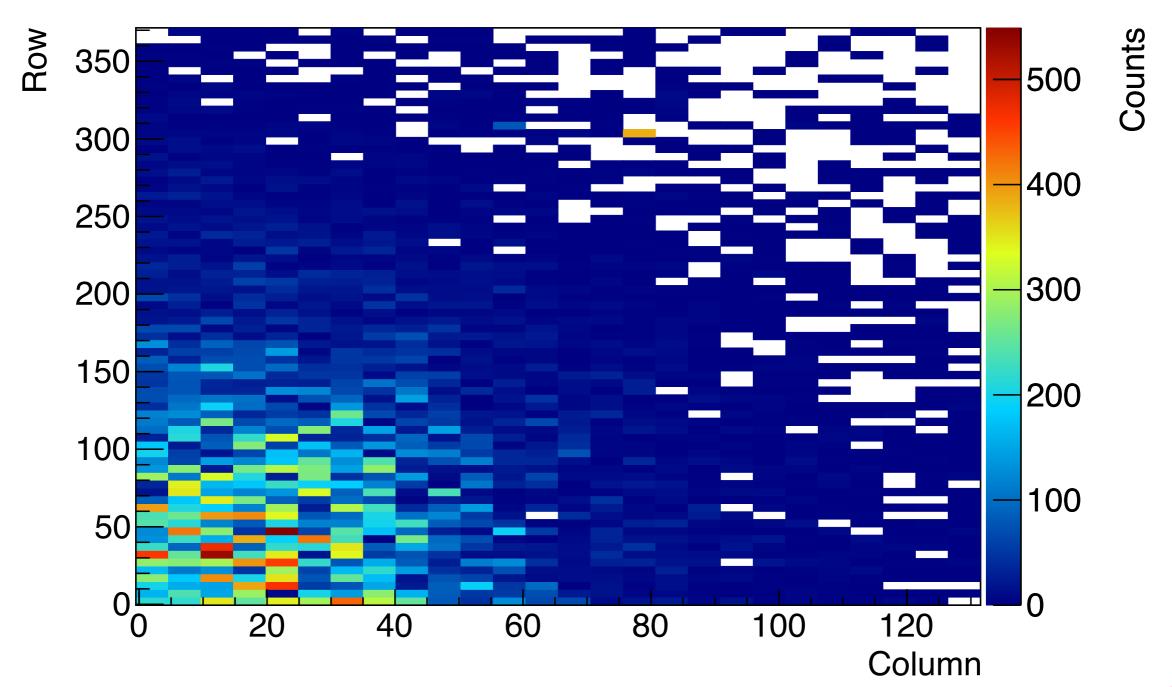

Using un-triggered digital readout, a **threshold scan** was performed for the whole matrix

Untuned matrix, GDAC setting

<sup>55</sup>Fe signal equals a charge injection of about 300mV (measured on this sensor)

**1 σ noise** value corresponds to **80 e**<sup>-</sup>

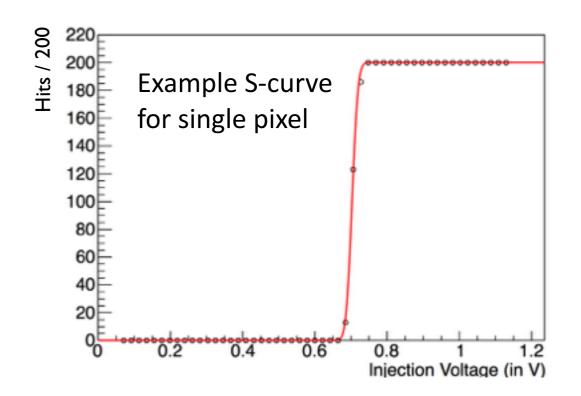

## **Tuning of Pixel Matrix**

Threshold map, 2350 untuned sensor 300 250 All 49104 200 pixels work ! 150

Writing of the pixel memories is working and the detection **threshold changes linearly** with the TDAC setting

Threshold tuning:

Detection thresholds are adjusted to  $\mu$ +3 $\sigma$  of untuned distribution

**Subset**: conducted for 2 rows (in total 264 pixels):

Distribution width ~3× smaller

$\sigma_{trimmed}$  = 9.5mV  $\leftrightarrow$  ~ 50 e<sup>-</sup>

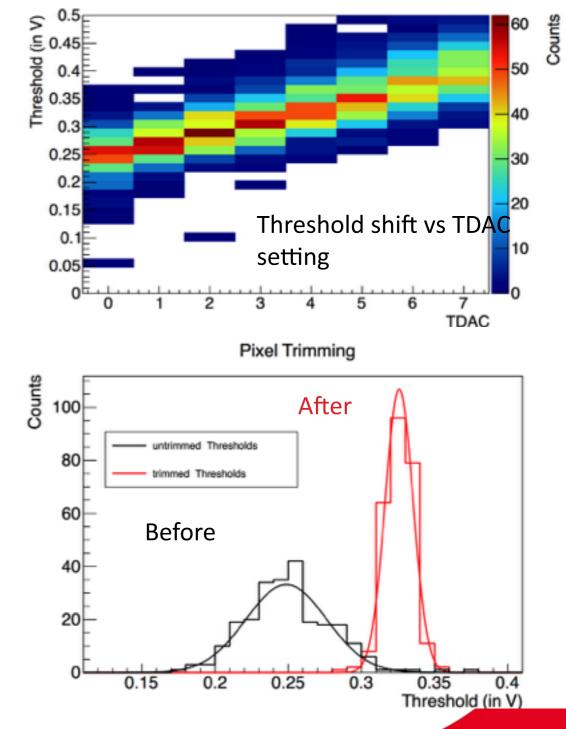

### **Signal Detection**

A <sup>55</sup>Fe source was held over the corner of an ATLASPix3 sensor.

**Chinese Foundry?**

#### SMIC MPW Shuttle Schedule

MPW Notice To serve all customers smoothly, following items must be noticed:

1. Only standard Process/Layers products can attend MPW. No bumping, No Bank and No Corner Split allowed.

On one shuttle, 4 seats (including sub-chip in one seat) are the maximum that one customer can get.

MPW only provides 50 dies for function verification.

MPW only provides 50 dies for function verification.

Shuttles are subject to cancellation if there are not enough passengers on board.

Without completion of below items before shuttle start date, shuttle reservation will not be held!

Quotation should be ready/ DRC must be clean/ SMIC IP merge case must be closed (related information need to be submitted at least 3 days before shuttle start date)

GDSII and tape out forms all need to be Approved by mask shop/ PTOS should be Approved

SMIC dicing size limit: 1500um < X < 12000um, 1500um < Y < 12000um.</li>

For 300mm shuttle, suggest use metal scheme condition: 6(MI-M6)+TM1(9kA)+14.5kA ALPA+12mil BG.

Opending MW booked cases will be cancelled within 90 days after schedie to the text.

8. Overdue MPW booked cases will be cancelled within 90 days after shuttle start.

| Tech Node   | IO Voltage/Tech Type/Char                                                                               | RF |                 | 2020 MPW Booking Cut-Off Date |                  |                  |                  |                  |                  |                  |                  |                  |                  |                 |

|-------------|---------------------------------------------------------------------------------------------------------|----|-----------------|-------------------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|-----------------|

| rech Node   | to voltage/ rech Type/char                                                                              | RP | Jan             | Feb                           | Mar              | Apr              | May              | Jun              | Jul              | Aug              | Sep              | Oct              | Nov              | Dec             |

| 14nm        | IO=1.8V<br>CMOS Logic (GE GP)                                                                           |    |                 |                               | 10<br>Q67 (Fab8) |                  |                  | 9<br>Q6P (Fab8)  |                  |                  | 8<br>Q6Z (Fab8)  |                  |                  | 8<br>Q7C (Fab8  |

| 28nm        | IO=1.8V   IO=2.5V<br>CMOS Logic (HP)                                                                    | Y  |                 |                               | 3<br>Q6D (Fab2)  |                  |                  | 2<br>Q6Q (Fab2)  |                  |                  | 1<br>Q6Y (Fab2)  |                  |                  |                 |

|             | IO=2.5V<br>CMOS Logic (LL[UP)                                                                           | Y  |                 | 4                             |                  |                  | 5                |                  | 7                |                  |                  | 13               |                  | 1               |

| 40nm        | IO=8/32V<br>CMOS High Voltage (HV)                                                                      |    |                 | Q69 (Fab2)                    |                  |                  | Q6K (Fab2)       |                  | Q6T (Fab2)       |                  |                  | Q73 (Fab2)       |                  | Q79 (Fab2)      |

|             | IO=1.8V  IO=2.5V<br>Adv. Emb-Flash (Cu-BEOL with AL-<br>TM2 + RDL process) (LL)                         |    |                 |                               |                  |                  |                  | 23<br>Q6R (Fab2) |                  |                  |                  |                  |                  | 15<br>Q7B (Fab2 |

|             | IO=2.5/5V   IO=2.5V<br>Adv. Emb-Flash (Cu-BEOL) (LL)                                                    |    |                 |                               |                  |                  | 12<br>Q6M (Fab2) |                  |                  |                  |                  |                  | 10<br>Q77 (Fab2) |                 |

| 55nm        | IO=1.8/2.5V   IO=1.8V   IO=2.5V<br>CMOS Logic (LL)                                                      | Y  |                 | 11                            |                  | 7                |                  |                  | 14               |                  |                  | 20               |                  |                 |

|             | IO=6/32V   IO=8/32V<br>CMOS High Voltage (HV)<br>Do not support 2/TM(STM)                               |    |                 | Q6C (Fab2)                    |                  | Q6G (Fab2)       |                  |                  | Q6U (Fab2)       |                  |                  | Q74 (Fab2)       |                  |                 |

| 0.11um      | IO=3.3V<br>Adv. Emb-Super flash (AL-BEOL) (LL)                                                          |    |                 |                               |                  |                  |                  |                  |                  |                  | 8<br>Q70 (Fab1)  |                  |                  |                 |

| 0.13um      | IO=3.3/5V  IO=5V<br>Adv. Emb-EEPROM (Cu-BEOL) (LL)                                                      |    |                 |                               |                  |                  |                  |                  |                  | 4<br>Q6V (Fab1)  |                  |                  |                  |                 |

| 0.11/0.13um | IO=3.3V<br>CMOS Logic (GE)   Mixed Signal (GE)                                                          | Y  |                 | 4<br>Q68 (Fab1)               |                  | 14<br>Q6H (Fab1) |                  | 30<br>Q6S (Fab1) |                  | 11<br>Q6W (Fab1) |                  | 27<br>Q75 (Fab1) |                  | 29<br>Q7D (Fab1 |

| 0.153um     | IO=3.3V<br>CMOS Logic (GE) Mixed Signal (GE)                                                            | Y  |                 |                               |                  |                  |                  |                  |                  | 18<br>Q6X (Fab1) |                  |                  |                  |                 |

| 0.18um      | IO=5/6/9/12/16/20/24/30/35/40<br>BCD V3E (EP)                                                           |    |                 |                               | 3<br>Q6E (Fab1)  |                  |                  |                  |                  |                  | 15<br>Q71 (Fab7) |                  |                  |                 |

|             | IO=3.3V<br>CMOS Logic (GE) Mixed Signal (GE)                                                            | Y  | 1<br>Q68 (Fab1) |                               |                  |                  | 19<br>Q6N (Fab1) |                  |                  |                  | 15<br>Q72 (Fab1) |                  |                  |                 |

| 0.18um      | IO=3.3V<br>CMOS Logic (GE)   Mixed Signal (GE)<br>IO=5/10/12/20/35/40V<br>BCDM (BCDM do not support RF) | Y  |                 |                               | 10<br>Q6F (Fab7) |                  |                  |                  | 21<br>Q6J (Fab7) |                  |                  |                  | 17<br>Q78 (Fab7) |                 |

|             | IO=3.3/5V  IO=5V<br>EEPROM Embedded (GE)                                                                |    |                 |                               |                  | 14<br>Q6L (Fab1) |                  |                  |                  |                  |                  | 27<br>Q76 (Fab7) |                  |                 |

2020 new offered feature: 40nm EF/0.11um EF

Version: 1.1 Update Date: 2019-10-15

Note: Hease login SMIC-Now to find the most updated MPW schedule. (後登很Smic-Now(()在间最影MPW Schedule.)

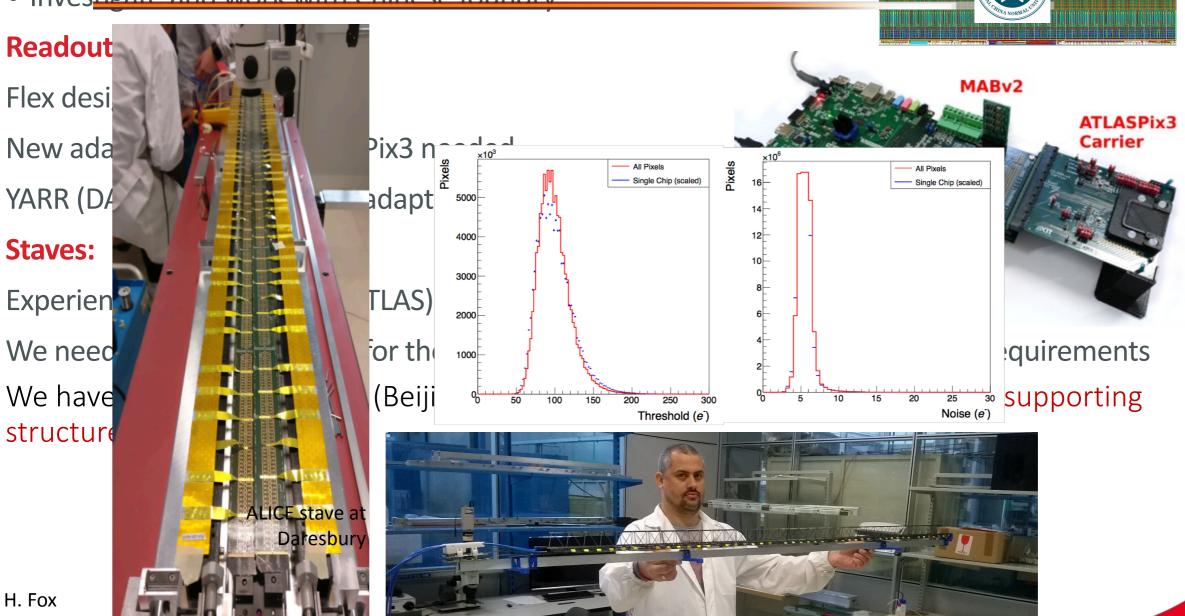

## **Module Flex**

#### Università and INFN di Milano: Attilio Andreazza, Mauro Citterio, Fabrizio Sabatini

Purpose is to build a **pseudo-quad module** for ATLAS Test system functionality for large size detectors

Starting point is the ATLASPix3 single-chip card produced by KIT and used for the tests

#### Two basic ideas:

- Connector

- Integrated Pigtail

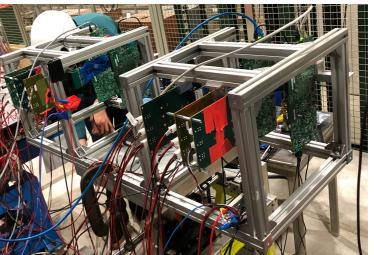

## DAQ: YARR Yet Another Rapid Readout

https://iopscience.iop.org/article/ 10.1088/1742-6596/898/3/032053

YARR is a small **self-contained DAQ system**. Linux PC with a x4 **PCIe slot for the FPGA card**

FPGA card: e.g. **Trenz TEF1001**, XpressK7,... **FMC cards** for FE-I4 and RD53A

Up to **1.6GBit/s possible** with this setup.

We have used the YARR readout with a digital RD53A module in **Lancaster & Edinburgh**.

**Todo:** Adaptation to ATLASPix3 necessary:

- FMC

- Software

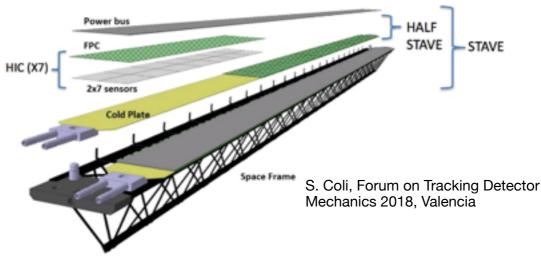

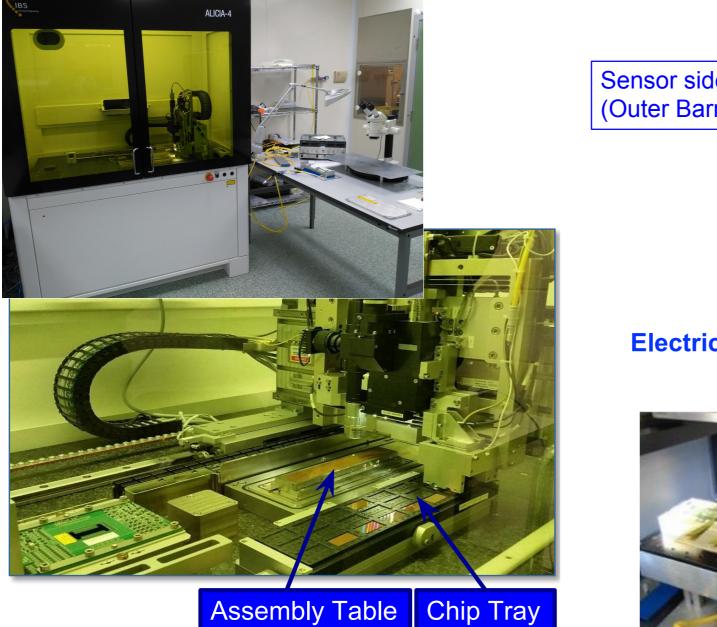

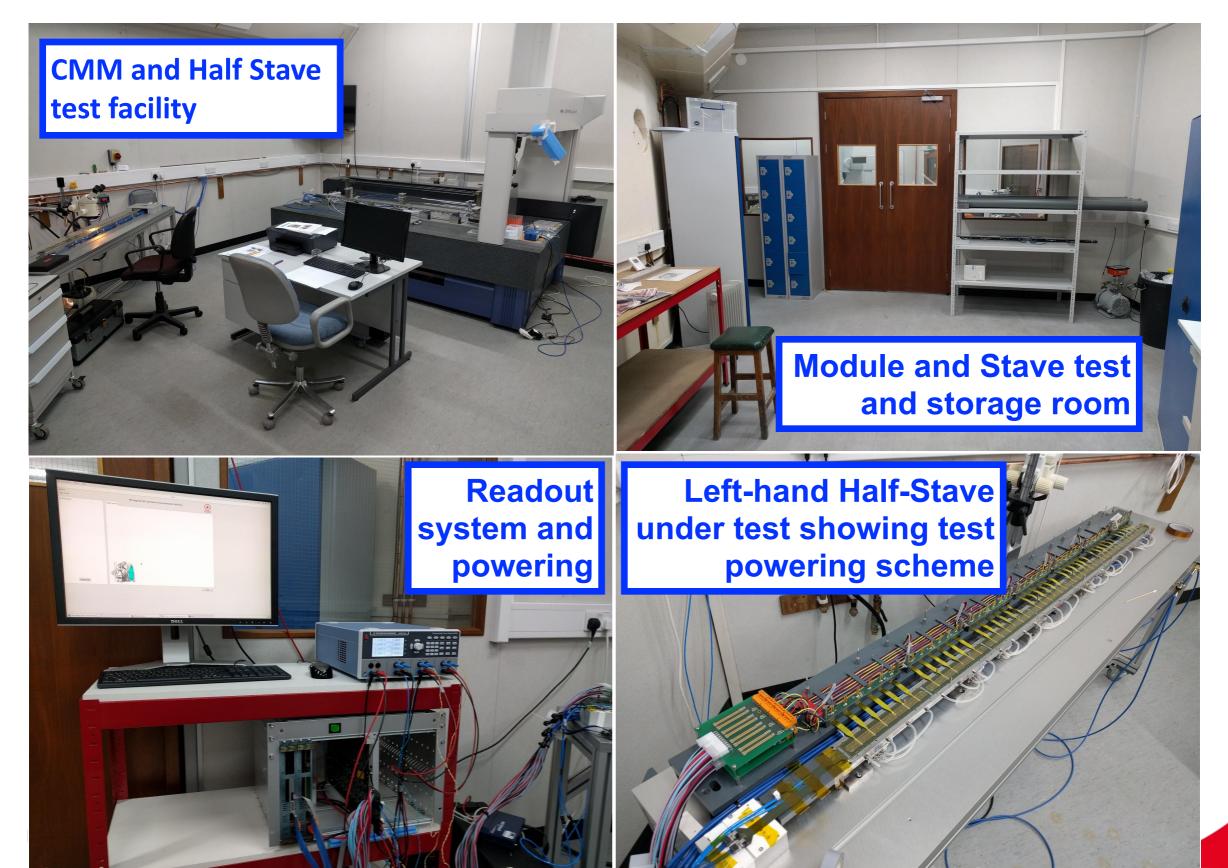

## **ALICE: Outer Barrel Module Assembly**

Liverpool (Prof. Marielle Chartier) with Daresbury are responsible for the construction of 500 modules (incl. spares) for the Outer Layers (until early 2019).

In partnership with Bari (IT), Strasbourg (FR), Pusan (KR), Wuhan (CN). Production in the Liverpool Semiconductor Detector Centre finished.

6 machines distributed to different construction sites

Sensor side (Outer Barrel)

**Electrical Interconnection** (wire bonding)

14

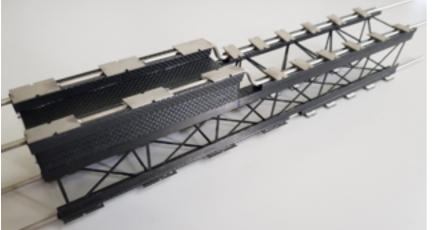

## **ALICE: Outer Barrel Stave Assembly**

Daresbury is responsible for the **construction of 22 Staves for the Outer Layers**.

Production in the Engineering Technology Centre **finished** well within time this year. In partnership with Torino & Frascati (IT), NIKHEF (NL), Berkeley (USA).

**Space Frame**

## ALICE: Stave Assembly and Testing at Daresbury

Daresbury Engineering Technology Centre

#### **Interested Groups in China**

Several Chinese institutions have expressed interests in the CMOS out tracker concept, including

- IHEP & Tsinghua sensor/module assembly & tests, on-going activities on ATLAS ITk-Strip and LHCb UT, JadePix design & characterization for CEPC

- USTC readout electronics, e.g. FELIX for the ATLAS Phase II upgrade and more

- SDU ASIC design, e.g. SUPix, and test system

- CCNU module assembly, delivery of ALICE ITS modules

- ... more

Explore the synergy with LHCb – "mighty" tracker, on which Chinese groups have expressed strong interests

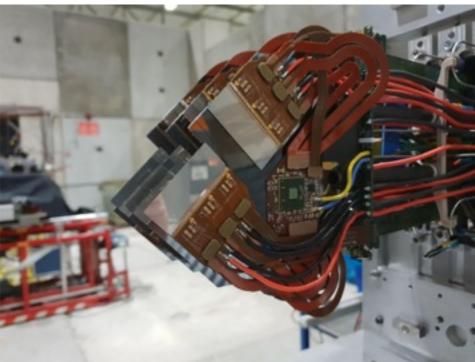

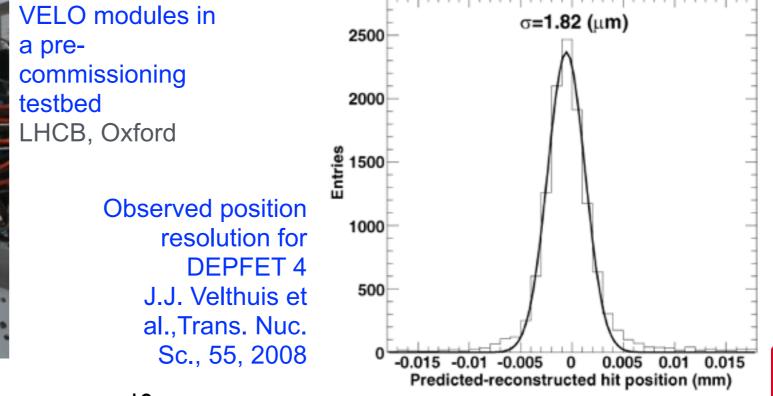

## Interested Groups in the UK: Bristol

Made significant contribution to the **TimePix3 telescope**

- Online Data Quality monitoring

- Slow control (HV & motor stages)

Did a large part of the **test beam** data analysis for the **Velo upgrade** modules

Did a large part of the **bench tests** for the **Velo upgrade modules**

Ran successful **test beam campaigns and bench tests** for **CMOS sensors** towards ILC (FORTIS, TPAC, ISIS, HEPAPS4)

Built the Aida Trigger Logic Unit

Before performed testbeams with **DEPFET, ATLAS Diamond pixel sensors and 3D sensors**

## Interested Groups in the UK: Liverpool

The Liverpool **HV-CMOS work** includes generic development work for **RD50** as well as our involvement in the development of the **MuPix chips** for Mu3e and **AtlasPix** and work on HV-CMOS for medical applications. Currently, non of these have a particular focus on CEPC.

See Tim Jones' talk on Light-weight Mechanics in this session.

#### **ALICE colleagues** in Liverpool

There is also **DAQ experience in the UK** with interest in **Bristol**, **RAL** (see **Jens Dopke's talk**) and **RHUL**.

#### D. Bortoletto

PWELL NWELL

2

Pixel Sensor Digital Analog input capacitance (< 5 fF) ➡ high SNR 20 mm Small depletion depth (~20  $\mu$ m) MALTA Collection 22 mm electrode Modified process to ensure full lateral 36.4 µm depletion TRANSISTORS n-well n-well NMOS PMOS NMOS p-well p-well n-well Deep p-well Process with n- gap Modified **S**3 **S7** gap in n-**Mini-MALTA** standard. < > **PMOS S2 S6** reset Process plus additional Modified DPW extra-deep **S1 S5** .... p-well ത Mini-MALTA: Probing Mini-MALTA on carrier board n-well gap and deeper standard **SO S4** Modified Process LOW DOSE N-TYPE IMPLAN p-well wafer process DEPLETED ZONE standard front-end enlarged transistors modifications

TowerJazz 180 nm CMOS technology Oxford

Used in ALICE ITS

ATLAS ITK

13/11/19

- Small collection electrode (3  $\mu$ m<sup>2</sup>)

MALTA: full demonstrator size sensor. Novel asynchronous readout architecture

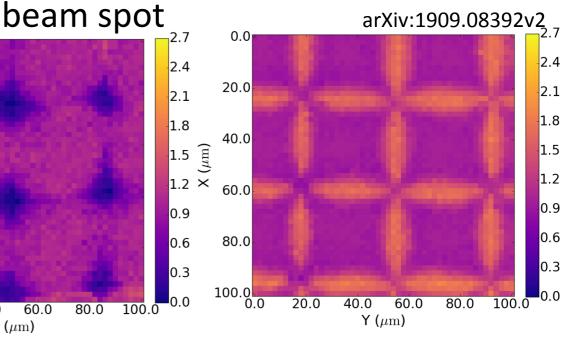

# Sensor R&D and Future Plans Oxford

0.0

20.0

40.0

60.0

80.0

100.0

600

Threshold [e]

20.0

40.0

MALTA after

$1e15 \text{ neq/cm}^2$

Y (μm)

60.0

80.0

#### **Characterisation measurements:**

- I-V, Noise, Threshold, Gain, Source Response

- Test-beams at SPS, Diamond RAL, DESY & ELSA.

W2R1+W4R2 (1×10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup>

DFSY

X-Ray test beam measurements at Diamond Light Source with 2 µm

#### miniMALTA n-gap after 1e15 neq/cm<sup>2</sup>

#### **Plans:**

100

Efficiency [%]

95

90

**85**F

**80**

75⊟

70

**65**

**60**

55Ŀ

50<sup>t</sup>

En

(30 25

○ ○ Large trans.

Std trans.

$\triangle$   $\triangle$  Large trans. + extra p-well

▲ Std trans. + extra p-well

300

Large trans. + n gap

Std trans. + n gap

200

W4R2

Engineering of new substrates (e.g.: Czochralski)

400

new version of MALTA that will be aimed for testbeams, targeting the AIDA telescope framework

arXiv:1909.11987v1

500

## **Summary and Conclusion**

#### Sensor:

Functional ATLASPix3 sensor available for prototyping Optimisation for a (Chinese)  $e^+e^-$  collider

- Power consumption

- Investigate and work with Chinese foundry

# 10000-li project

## 10000-li project

## 200-li should be easy!

# Backup

### Backup: Radiation lengths X/X<sub>0</sub>

#### CDR: FST: 5-7% FST2 7-10% X0

Physics | Lancaster University

#### Alice: 0.8% X0/layer for outer barrel

| Stave element | Component             | Material      | Thickness<br>(µm) | $\begin{array}{c} X_0 \\ (\mathrm{cm}) \end{array}$ | $X_0$ (%) |

|---------------|-----------------------|---------------|-------------------|-----------------------------------------------------|-----------|

| Module        | FPC Metal layers      | Aluminium     | 50                | 8.896                                               | 0.056     |

|               | FPC Insulating layers | Polyimide     | 100               | 28.41                                               | 0.035     |

|               | Module plate          | Carbon fibre  | 120               | 26.08                                               | 0.046     |

|               | Pixel Chip            | Silicon       | 50                | 9.369                                               | 0.053     |

|               | Glue                  | Eccobond 45   | 100               | 44.37                                               | 0.023     |

| Power Bus     | Metal layers          | Aluminium     | 200               | 8.896                                               | 0.225     |

|               | Insulating layers     | Polyimide     | 200               | 28.41                                               | 0.070     |

|               | Glue                  | Eccobond 45   | 100               | 44.37                                               | 0.023     |

| Cold Plate    |                       | Carbon fleece | 40                | 106.80                                              | 0.004     |

|               |                       | Carbon paper  | 30                | 26.56                                               | 0.011     |

|               | Cooling tube wall     | Polyimide     | 64                | 28.41                                               | 0.013     |

|               | Cooling fluid         | Water         |                   | 35.76                                               | 0.105     |

|               | Carbon plate          | Carbon fibre  | 120               | 26.08                                               | 0.046     |

|               | Glue                  | Eccobond 45   | 100               | 44.37                                               | 0.023     |

| Space Frame   |                       | Carbon rowing |                   |                                                     | 0.080     |

| Total         |                       |               |                   |                                                     | 0.813     |

26

## ATLASPix3: Threshold and Noise Measurements

Example Noise vs Threshold distribution: